# Development of device isolation technologies for GaN-based field-effect transistors

室化ガリウムトランジスタにおける 素子間分離技術の研究

江瀅

**Ying Jiang**

徳島大学 Tokushima University

2015年9月

#### **Abstract**

Gallium nitride (GaN) semiconductor has the great advantage in the application of hightemperature and high-frequency power electronic devices owing to its unique properties, such as wide band-gap, high electron saturation velocity, high breakdown field and high electron conductivity of the two-dimensional electron gas (2DEG) in AlGaN/GaN heterostructure. AlGaN/GaN heterojunction field-effect transistor (HFET) and GaN metal-oxide-semiconductor field-effect transistor (MOSFET) are the classic devices of GaN-based field-effect transistors (FETs), which can be applied to microwave amplifying devices for wireless communication, military radar and power conversion devices for motor inverter. Device isolation is one of the primary processes for the fabrication of GaN-based FETs, and mesa structure is often adopted for device isolation through dry etching. However, dry etching damages increases high surface leakage current of the mesa-isolated region, leading to a high off-state current and power loss of AlGaN/GaN HFET. For the mesa-isolated linear GaN MOSFET, field isolation is impossible because a parasitic MOSFET exists in the mesa-isolated region, which widens the effective channel width, resulting in an overestimated mobility. Hence, developing the device isolation processes for AlGaN/GaN HFETs, field isolation processes for GaN MOSFET, and evaluating the isolation effectiveness of these processes are essential for GaN-based FETs.

In this thesis, evaluation technology of isolation effectiveness was investigated on the basic of fabrication processes and test methods for AlGaN/GaN HFET and GaN MOSFET. The effective O<sub>2</sub> plasma treatment process was established, the oxidation mechanism was analyzed, and isolation effectiveness of AlGaN/GaN HFETs with O<sub>2</sub> plasma treatment were characterized and evaluated. The boron field implantation for GaN MOSFET was developed, the elimination of the parasitic MOSFET in the isolation region was examined using electrical testing of several MOSFET structures, and the field isolation effectiveness of GaN MOSFET and the influence of implantation damage on device performance for different isolation structures were characterized and evaluated. The contents and conclusions of this thesis are as follows:

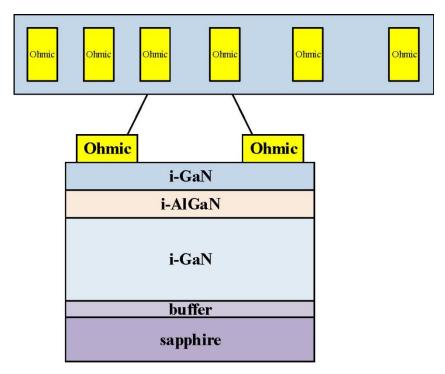

In chapter 2, the basic fabrication processes, test methods and evaluation technology of isolation effectiveness for AlGaN/GaN HFET and GaN MOSFETs were studied. On the basis of the fabrication processes of GaN-based FETs, device performances were characterized through the current-voltage (*I*–*V*) and capacitance-voltage (*C*–*V*) measurements, and the processes isolation effectiveness was evaluated through the transmission line model (TLM) structure and special MOSFETs fabricated in the isolation regions. In the TLM structure, the regions between every two ohmic electrodes were formed by different isolation processes, and the processes isolation effectiveness were evaluated by sheet resistance measurements or *I*–*V* characteristics of these regions. The circular MOSFETs were fabricated in the isolation regions to examine the existence of a parasitic MOSFET by *I*–*V* characteristics. The circular and linear MOSFETs with same fabrication processes were fabricated, the effectiveness of isolation

processes was evaluated through comparing their transfer characteristics, and the effect of field implantation on device performance was investigated through calculating the field-effect electron mobility and the density of interface traps ( $D_{it}$ ) at SiO<sub>2</sub>/GaN interface.

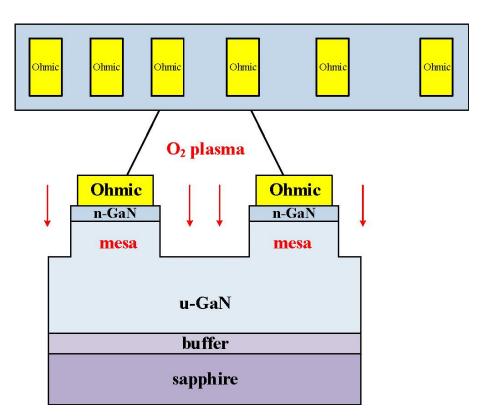

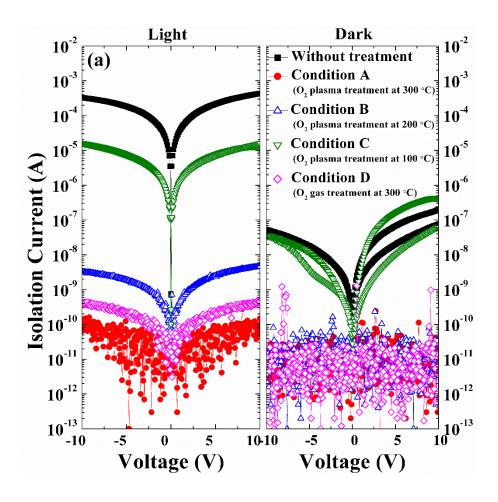

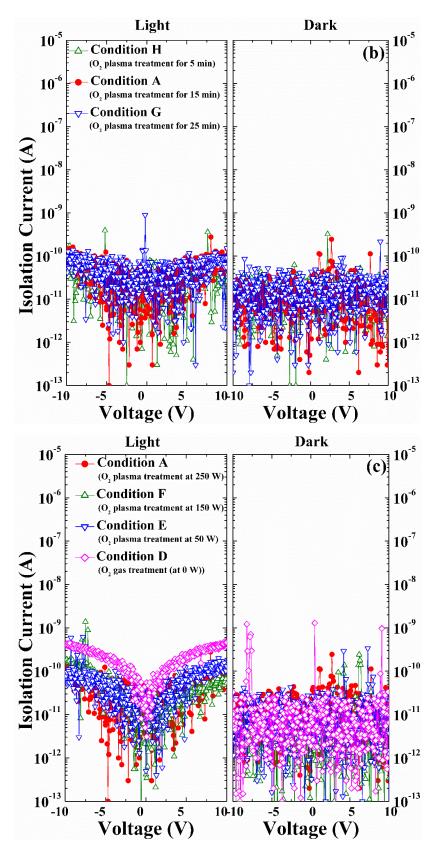

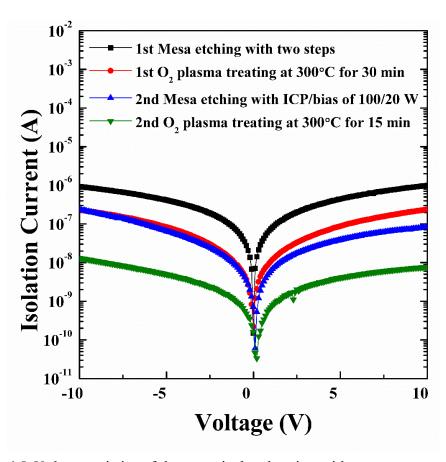

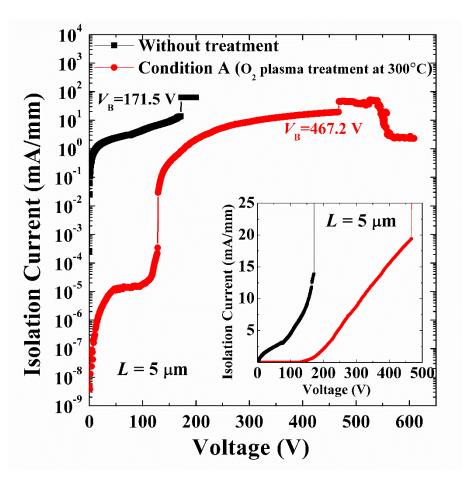

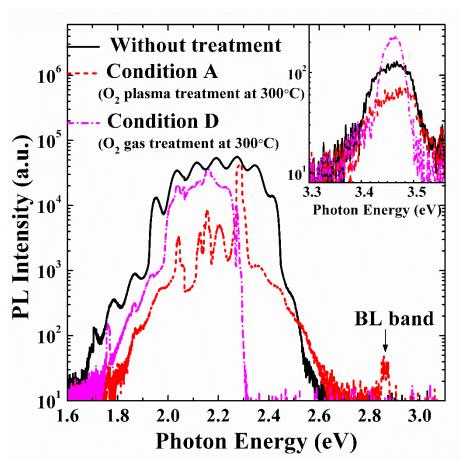

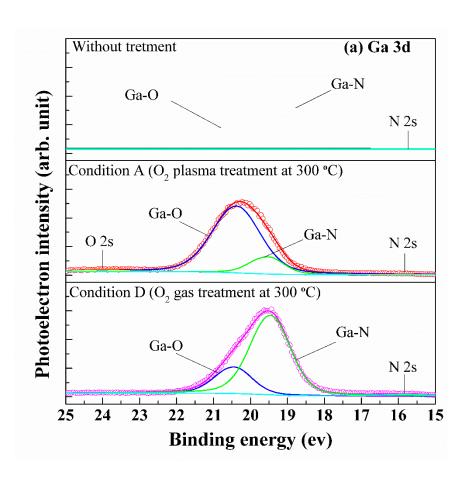

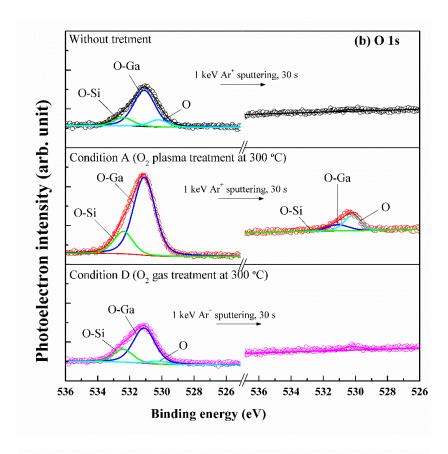

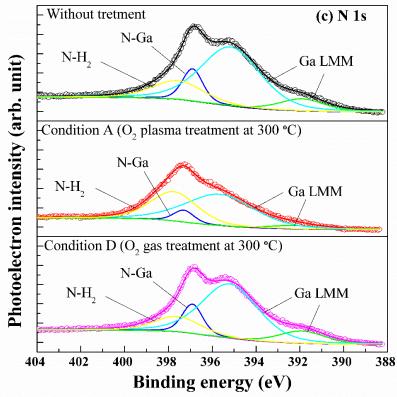

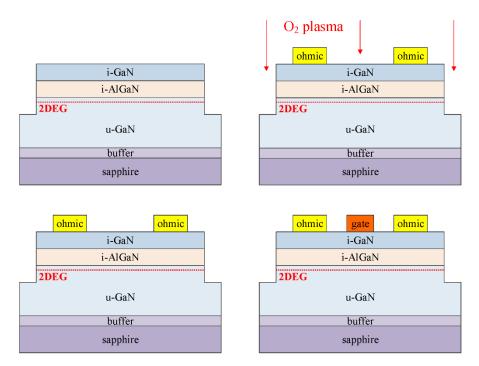

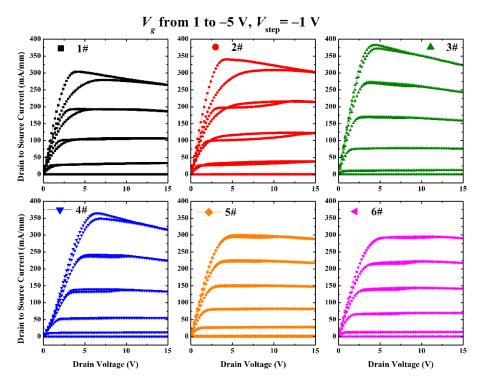

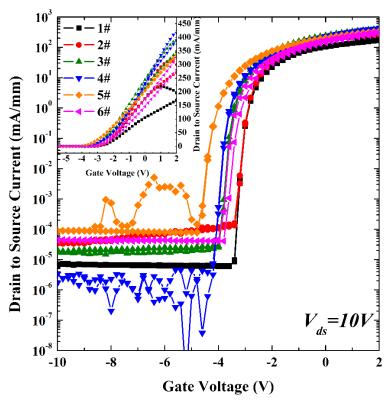

In chapter 3, the isolation effectiveness and oxidation mechanism of O<sub>2</sub> plasma treatment for AlGaN/GaN HFETs were studied. The process of O<sub>2</sub> plasma treatment on the mesa-isolated region of AlGaN/GaN HFETs was adopted, the optimal condition was established by I-V measurement on TLM structure, the oxidation effectiveness and mechanism of the mesa etching surface were analyzed through photoluminescence (PL) spectrum and X-ray photoelectron spectroscopy (XPS), and AlGaN/GaN HFETs with O<sub>2</sub> plasma treatment were fabricated and characterized. The I-V results of TLM structure indicated that the isolation current were strongly dependent on treatment temperature and the depth of etching damage. Treatment at 300 °C was confirmed to be the optimal condition, under which isolation current was reduced by four orders of magnitude to  $10^{-11}$  A and photovoltaic response was suppressed, and the breakdown voltage of the mesa-isolated region increased from 171.5 to 467.2 V. The PL spectrum analysis showed a decrease in the density of defects related to the yellow luminescence band and the occurrence of defects related to the blue luminescence band. XPS results showed that O<sub>2</sub> plasma treatment can form high amounts of Ga<sub>2</sub>O<sub>3</sub> than O<sub>2</sub> gas treatment, and the defect of substitutional oxygen on the nitrogen site was probably formed. The -Vcharacteristics of AlGaN/GaN HFETs presented a high on/off drain current ratio of  $1.73 \times 10^7$ .

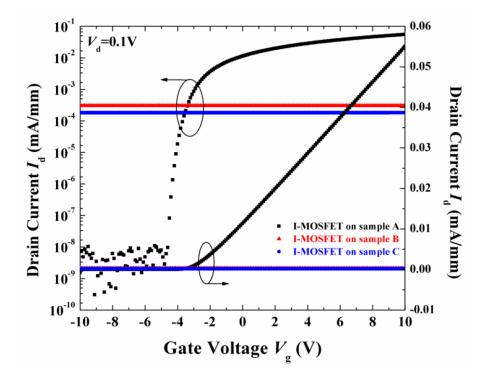

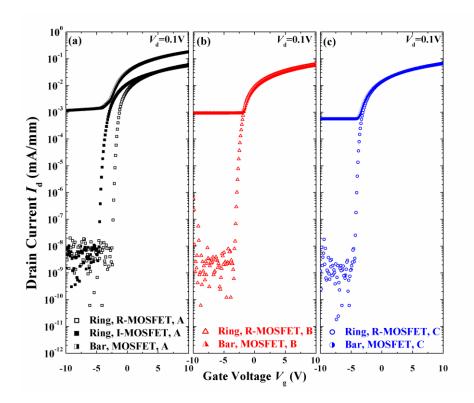

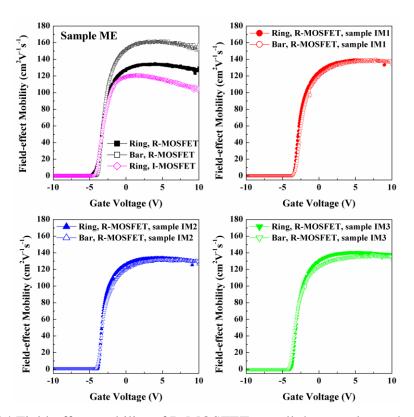

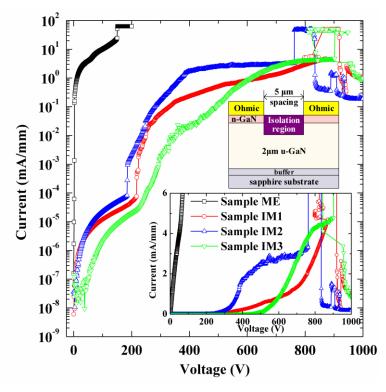

In chapter 4, the isolation effectiveness and influence of implantation damage on device performance for boron ion implantation process in GaN MOSFETs were studied. The process of boron field implantation was developed and improved for GaN MOSFETs, the elimination of parasitic MOSFETs was confirmed by the I-V characteristics of circular MOSFETs fabricated in the isolation regions, and isolation effectiveness of process was evaluated through the comparison of I-V characteristics between circular and linear device. The influence of implantation damage on device performance for different isolation structures were evaluated by the field-effect electron mobility and  $D_{it}$  according to I-V and C-V tests. The process of boron field implantation was altered and subsequently conducted after all the high-temperature processes, and implanted regions with high resistivity were achieved. The circular MOSFET fabricated in the isolation region presented an extremely low drain current of  $7 \times 10^{-8}$  mA/mm, demonstrating that the parasitic MOSFET in the isolation region was eliminated by boron field implantation. The off-state drain current of the linear MOSFET was reduced from  $3\times10^{-5}$ mA/mm of mesa isolation to  $6 \times 10^{-7}$  mA/mm of boron field implantation, which was only one order of magnitude higher than the  $7 \times 10^{-8}$  mA/mm of the circular device. Field isolation for GaN MOSFETs succeeded. The calculation of the field-effect electron mobility showed that implanting did not deteriorate the mobility. The  $D_{\rm it}$  results indicated that the isolation structure of both mesa and implantation did not influence the interface state density.

**Key words:** Gallium nitride; device isolation; field isolation; AlGaN/GaN HFET; GaN MOSFET

### **CONTENTS**

| Abstract                                                                         | I        |

|----------------------------------------------------------------------------------|----------|

| List of Figures and Tables                                                       | V        |

| Chapter 1 Introduction                                                           | 1        |

| 1.1 Material advantages of GaN                                                   | 1        |

| 1.1.1 Material growth and properties                                             | 1        |

| 1.1.2 Crystal structure                                                          | 4        |

| 1.1.3 Polarization effects and 2DEG                                              | 5        |

| 1.2 Overview of GaN-based field-effect transistors                               | 8        |

| 1. 2. 1 AlGaN/GaN HFET                                                           | 8        |

| 1. 2. 2 GaN MOSFET                                                               | 9        |

| 1. 3 Significance of device isolation                                            | 10       |

| 1. 3. 1 Device isolation of AlGaN/GaN HFET                                       | 10       |

| 1. 3. 2 Field isolation of MOSFET                                                | 12       |

| 1. 4 Motivation and objectives                                                   | 15       |

| 1. 5 Outline of dissertation                                                     | 16       |

| Chapter 2 Fabrication process, test methods and evaluation technology of Ga      | aN-based |

| FET                                                                              | 17       |

| 2. 1 AlGaN/GaN HFET                                                              | 17       |

| 2. 1. 1 Structures of AlGaN/GaN HFET                                             | 18       |

| 2. 1. 2 Fabrication process of AlGaN/GaN HFET                                    | 20       |

| 2. 1. 3 Test methods of AlGaN/GaN HFET                                           |          |

| 2. 2 GaN MOSFET                                                                  | 24       |

| 2. 2. 1 Structures of GaN MOSFET                                                 | 25       |

| 2. 2. 2 Fabrication process of GaN MOSFET                                        | 27       |

| 2. 2. 3 Test methods of GaN MOSFET                                               | 28       |

| 2. 2. 4 Fabrication of GaN MOSFET using BCl <sub>3</sub> etching gas             | 29       |

| 2. 3 Evaluation technology for device isolation                                  | 34       |

| 2. 3. 1 The structure of TLM and test methods                                    | 34       |

| 2. 3. 2 The structure of MOSFET and test methods                                 | 36       |

| 2. 4 Summary                                                                     | 37       |

| Chapter 3 O <sub>2</sub> plasma treatment for device isolation of AlGaN/GaN HFET | 38       |

| 3.1 O <sub>2</sub> plasma treatment process                                      | 38       |

| 3.1.1 Process flow of O <sub>2</sub> plasma treatment                                | 38        |

|--------------------------------------------------------------------------------------|-----------|

| 3.1.2 Selection of O <sub>2</sub> plasma treatment conditions                        | 39        |

| 3.1.3 The influence of O <sub>2</sub> plasma treatment on ohmic contacts             | 42        |

| 3.1.4 The influence of dry etching conditions on treatment results                   | 43        |

| 3.1.5 Breakdown characteristics of isolation region treated by O <sub>2</sub> plasma | 44        |

| 3.2 Analysis of oxidized etching surface                                             | 44        |

| 3.2.1 PL spectrum analysis                                                           | 45        |

| 3.2.2 XPS analysis                                                                   | 47        |

| 3.3 AlGaN/GaN HFET using O <sub>2</sub> plasma treatment                             | 50        |

| 3. 3. 1 Fabrication process flow of AlGaN/GaN HFET using O2 plasma trea              | tment 50  |

| 3. 3. 2 Characterization of AlGaN/GaN HFET using O2 plasma treatment                 | 51        |

| 3.4 Summary                                                                          | 55        |

| 4 Boron ion implantation as field isolation process for GaN MOSFET                   | 56        |

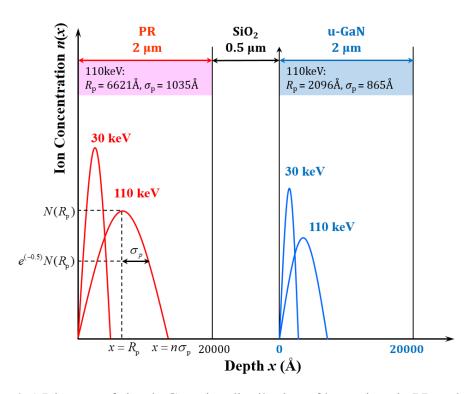

| 4.1 Simulation of ion implantation profile                                           | 56        |

| 4. 2 GaN MOSFETs with boron ion implantation                                         | 57        |

| 4. 2. 1 Fabrication process flow of GaN MOSFETs with boron ion implanta              | tion 57   |

| 4. 2. 2 Sheet resistance of implanted region                                         | 59        |

| 4. 2. 3 Evaluation of isolation effectiveness for GaN MOSFET                         | 60        |

| 4. 3 GaN MOSFETs with improved process of annealing and boron ion imp                | lantation |

|                                                                                      | 66        |

| 4. 3. 1 Fabrication process flow of improved GaN MOSFETs                             | 66        |

| 4. 3. 2 Evaluation of isolation effectiveness for improved GaN MOSFET                | 68        |

| 4. 3. 3 Characterization of GaN MOSFETs with boron ion implantation                  | avoiding  |

| annealing process                                                                    | 70        |

| 4. 4 Summary                                                                         | 73        |

| 5 Conclusion and future works                                                        | 75        |

| 5. 1 Conclusion                                                                      | 75        |

| 5. 2 Future works                                                                    | 76        |

| Reference                                                                            | 77        |

| Published Academic Theses during PhD Period                                          | 88        |

| Acknowledgment                                                                       | 90        |

## List of Figures and Tables

| Figure 1. 1 Equilibrium $N_2$ pressure over $GaN(s) + Ga(l)$ system based on Ref. [32] and melting      |

|---------------------------------------------------------------------------------------------------------|

| points TM from Ref. [34]. The dashed line was calculated for ideal gas [38] and the solid               |

| line was fitted with experimental data                                                                  |

| Figure 1. 2 Illustration of (a) zincblende lattice and (b) Gallium-face wurtzite lattice of GaN.        |

| 5                                                                                                       |

| Figure 1. 3 Band diagram of (a) seperating AlGaN and GaN; (b) the AlGaN/GaN heterostructure.            |

| 6                                                                                                       |

| Figure 1. 4 Scheme of sheet charge density, polarization directions and conduction band diagram         |

| of Ga-face AlGaN/GaN heterostructures                                                                   |

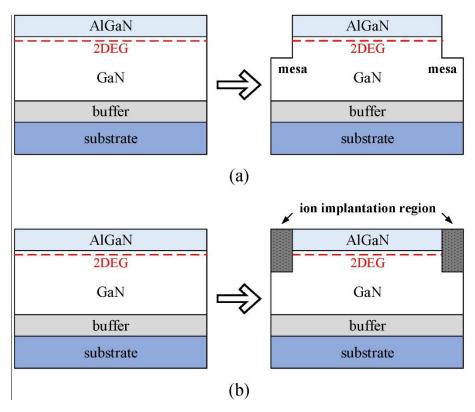

| Figure 1. 5 Schematic cross-section of (a) mesa structure and (b) ion implantation in                   |

| AlGaN/GaN heterojunction11                                                                              |

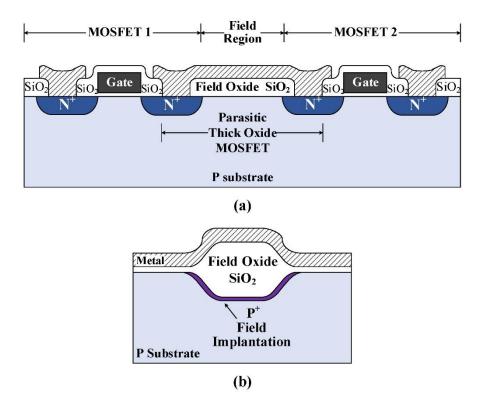

| $Figure 1.6Schematicof(a)theparasiticMOSFET-likedeviceinSiMOSFETICs[89];\\ (b)fieldMOSFETICs[89]$       |

| implantation and LOCOS isolation [71]                                                                   |

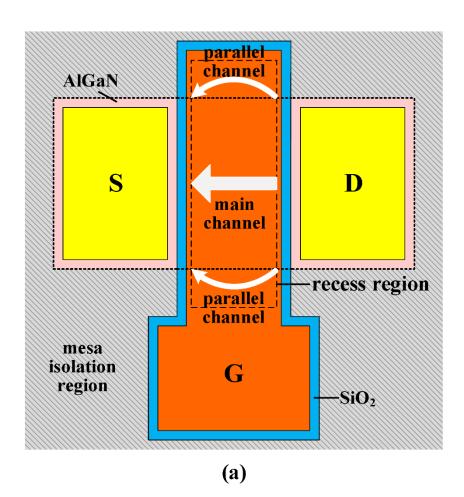

| Figure 1. 7 Schematic of (a) a long-channel linear and (b) a long-channel circular GaN MOSFET           |

| on AlGaN/GaN heterostructure                                                                            |

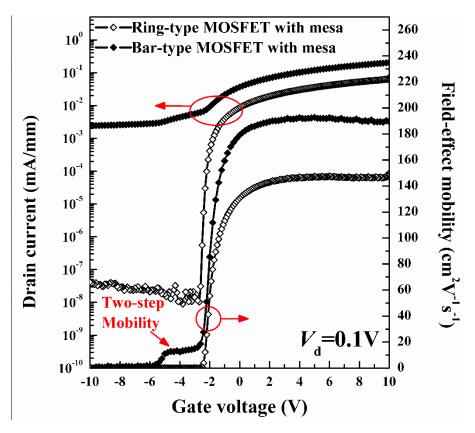

| Figure 1. 8 Transfer characteristics and field-effect electron mobility of a circular and a linear      |

| MOSFET. Both of devices were in the same recess condition and with only mesa isolation.                 |

|                                                                                                         |

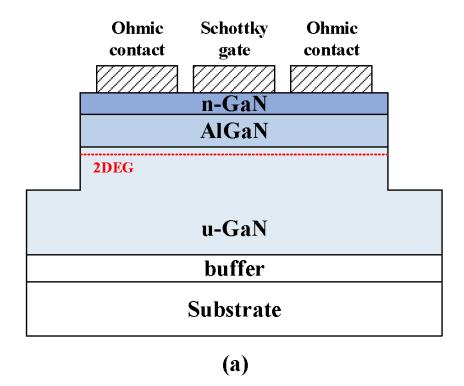

| Figure 2. 1 The cross section (a) and bird view (b) of a linear AlGaN/GaN HFET with mesa                |

| isolation. (c) shows MIS-gate and recessed-gate structures                                              |

| Figure 2. 2 The fabrication process of AlGaN/GaN HFET with mesa isolation 20                            |

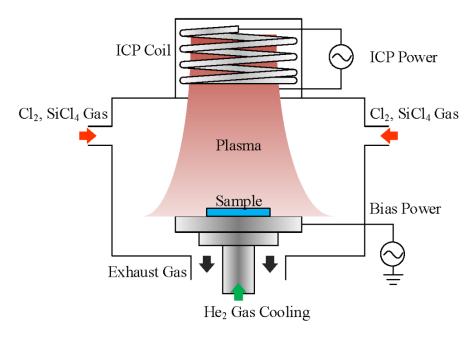

| Figure 2. 3 Schematic of internal components in the ICP system                                          |

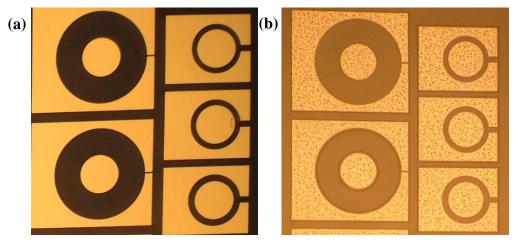

| Figure 2. 4 Pictures of (a) before 850 °C annealing and (b) after 850 °C annealing 22                   |

| Figure 2. 5 The picture of AlGaN/GaN HFETs after finishing the gate metallization.23                    |

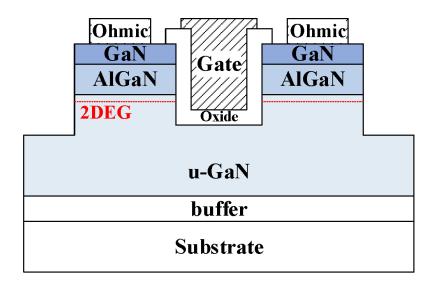

| Figure 2. 6 Schematic of recessed-gate structure for GaN MOSFET with mesa isolation. 25                 |

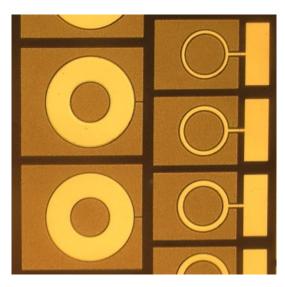

| Figure 2. 7 Schematic of long-channel linear and circular GaN MOSFET                                    |

| Figure 2. 8 The fabrication process of recessed-gate GaN MOSFET                                         |

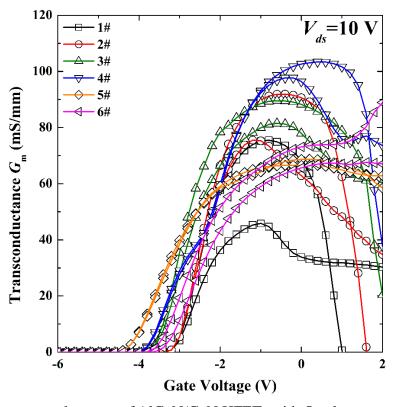

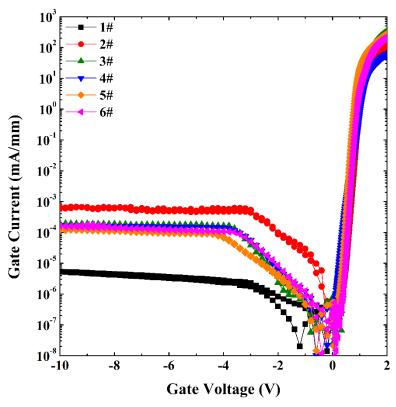

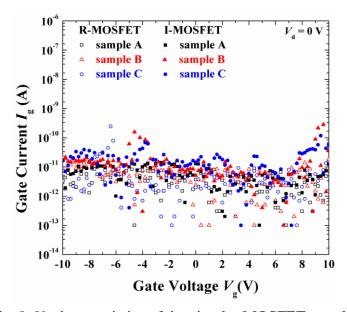

| Figure 2. 9 Gate leakage current of GaN MOSFETs of all the samples with gate voltage from –             |

| 10 to 10 V                                                                                              |

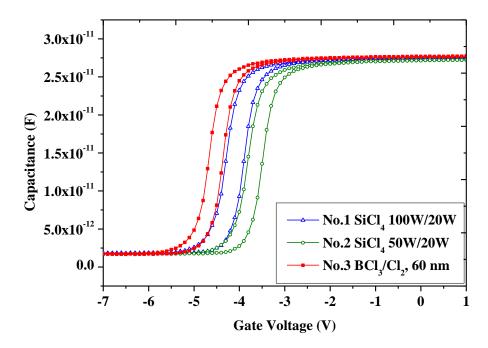

| Figure 2. 10 The segment of <i>C</i> – <i>V</i> characteristics curve of GaN MOSFETs of all the samples |

| with gate voltage from -7 to 1 V                                                                        |

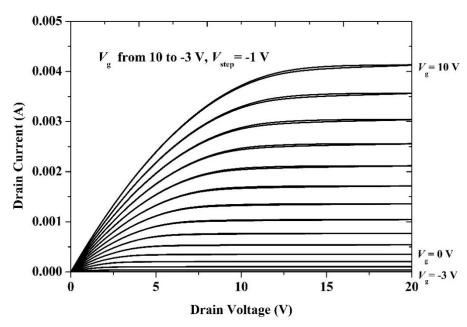

| Figure 2. 11 $I_d$ - $V_d$ characteristics of the device etched with BCl <sub>3</sub> gas and the recess depth of 60 |

|----------------------------------------------------------------------------------------------------------------------|

| nm                                                                                                                   |

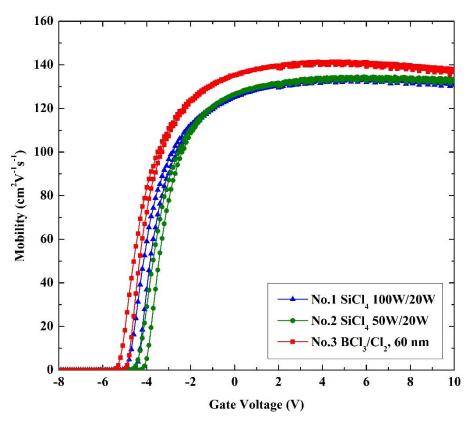

| Figure 2. 12 The field-effect mobility of GaN MOSFETs of all the samples 33                                          |

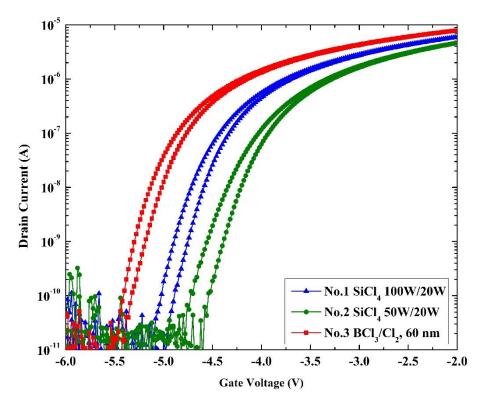

| Figure 2. 13 $I_{\rm d}$ - $V_{\rm g}$ characteristics of GaN MOSFETs of all the samples in the subthreshold region  |

|                                                                                                                      |

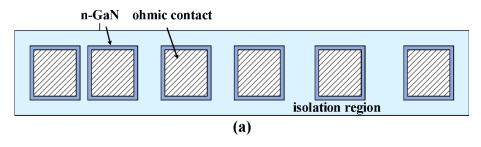

| Figure 2. 14 TLM for characterizing the isolation region. (a) top view; (b) cross-section view.                      |

|                                                                                                                      |

| Figure 2. 15 the fabrication processes of I-MOSFET with mesa isolation                                               |

| Figure 3. 1 The TLM structure for characterizing the mesa-isolated region                                            |

| Figure 3. 2 I-V characteristics of the mesa-isolated region with different conditions, (a) under                     |

| different temperature, (b) for different time, and (c) at different power 41                                         |

| Figure 3. 3 The TLM structure with 2DEG layer                                                                        |

| Figure 3. 4 <i>I–V</i> characteristics of the mesa-isolated region with two-step mesa etching. 43                    |

| Figure 3. 5 Breakdown characteristics of the mesa-isolated region without treatment and treated                      |

| by condition A                                                                                                       |

| Figure 3. 6 PL spectrum at room temperature of all the samples. The inset shows the near band-                       |

| edge luminescence band                                                                                               |

| Figure 3. 7 the core level spectra of Ga 3d, O 1s and N 1s for all the samples 49                                    |

| Figure 3. 8 The fabrication process of AlGaN/GaN HFET with mesa isolation and $O_2$ plasma                           |

| treatment                                                                                                            |

| Figure 3. 9 I-V characteristics of AlGaN/GaN HFETs with O2 plasma treatment on all the                               |

| samples                                                                                                              |

| Figure 3. 10 The transfer characteristics of AlGaN/GaN HFETs with O2 plasma treatment on                             |

| all the samples                                                                                                      |

| Figure 3. 11 The transconductance of AlGaN/GaN HFETs with $\mathrm{O}_2$ plasma treatment on all the                 |

| samples                                                                                                              |

| Figure 3. 12 The $I_g$ - $V_g$ characteristics of AlGaN/GaN HFETs with $O_2$ plasma treatment on all                 |

| the samples. 54                                                                                                      |

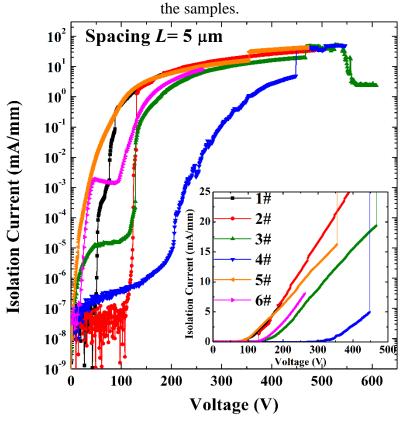

| Figure 3. 13 Breakdown characteristics of the mesa-isolated region treated by $O_2$ plasma on all                    |

| the samples                                                                                                          |

| Figure 4. 1 Diagram of simple Gaussian distribution of boron ions in PR and u-GaN.57                                 |

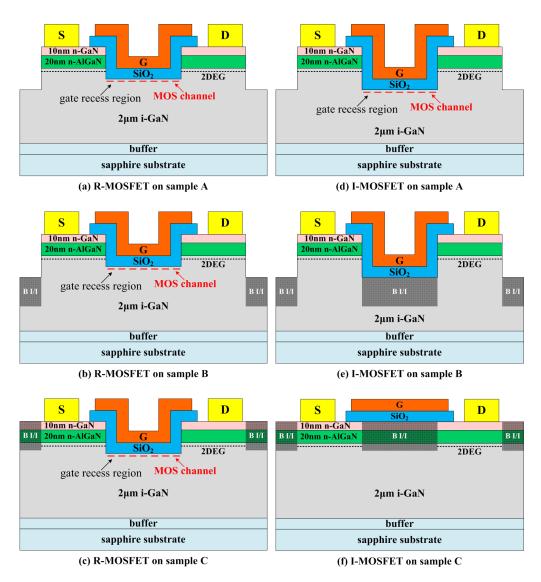

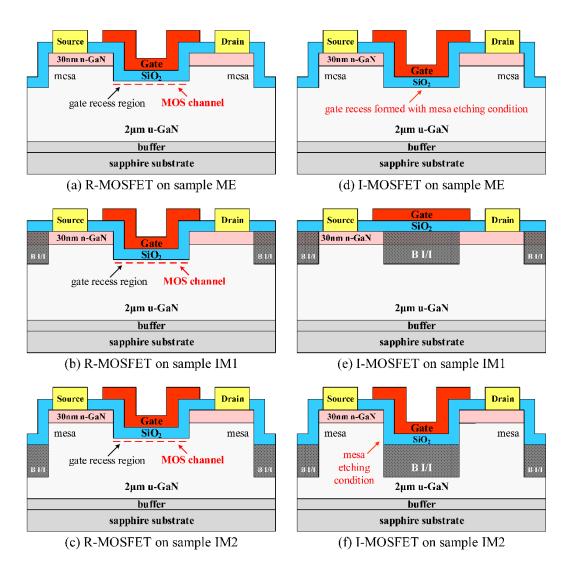

| Figure 4. 2 Schematic cross-section of (a)-(f): the R-MOSFETs and the I-MOSFETs of sample                            |

| A, B and C, respectively.                                                                   | 58                      |

|---------------------------------------------------------------------------------------------|-------------------------|

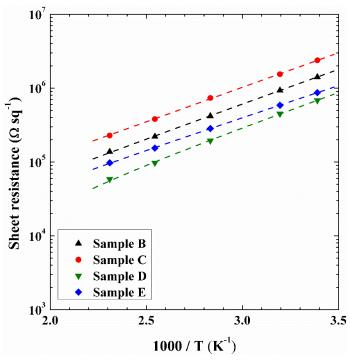

| Figure 4. 3 Measured sheet resistance of isolation regions at various temperature           | es 60                   |

| Figure 4. 4 The $I_g$ - $V_g$ characteristics of the circular MOSFETs on all the samples    | s 60                    |

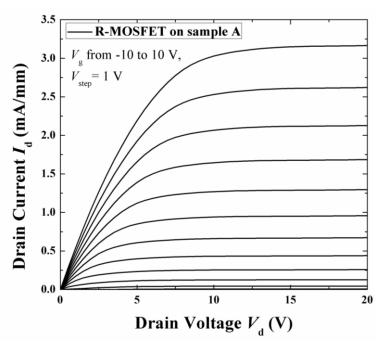

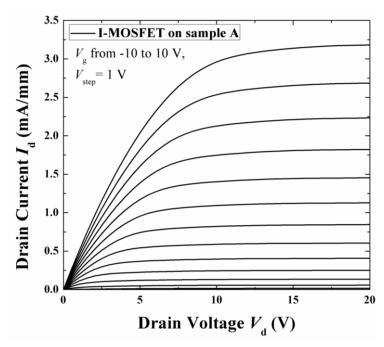

| Figure 4. 5 The $I_d$ - $V_d$ characteristics of a circular R-MOSFET on sample A with $g$   | gate voltage $V_{ m g}$ |

| from -10 to 10 V and step of 1 V.                                                           | 61                      |

| Figure 4. 6 The $I_d$ - $V_d$ characteristics of a circular I-MOSFET on sample A with §     | gate voltage $V_{ m g}$ |

| from -10 to 10 V and step of 1 V.                                                           | 62                      |

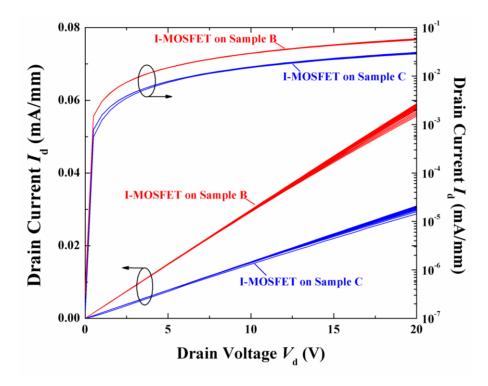

| Figure 4. 7 The $I_d$ - $V_d$ characteristics of circular I-MOSFETs on sample B and C       | with linear and         |

| logarithm plots                                                                             | 62                      |

| Figure 4. 8 The transfer ( $I_d$ - $V_g$ ) characteristics of the circular I-MOSFETs on all | the samples at          |

| V <sub>d</sub> of 0.1 V                                                                     | 63                      |

| Figure 4. 9 The comparison of the transfer characteristics between a linear and             | d a circular R-         |

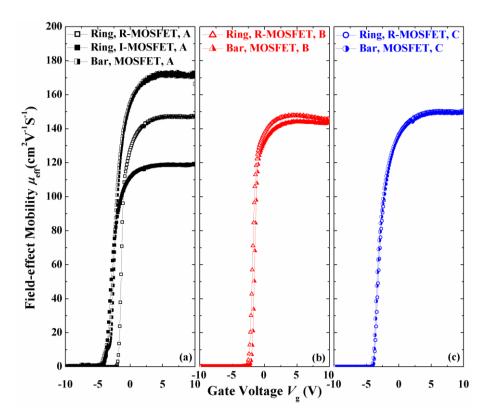

| MOSFET on (a) sample A, (b) sample B, and (c) sample C, at $V_d = 0.1 \text{ V}$            | 64                      |

| Figure 4. 10 The field-effect mobility of a linear and a circular R-MOSFET on s             | ample A (a), B          |

| (b), and C (c) comparing with that of circular I-MOSFET on sample A (a).                    | 65                      |

| Figure 4. 11 Structures of (a)–(c) ordinary recessed-gate R-MOSFETs and (d)–(               | f) I-MOSFETs            |

| fabricated on the different isolation regions.                                              | 67                      |

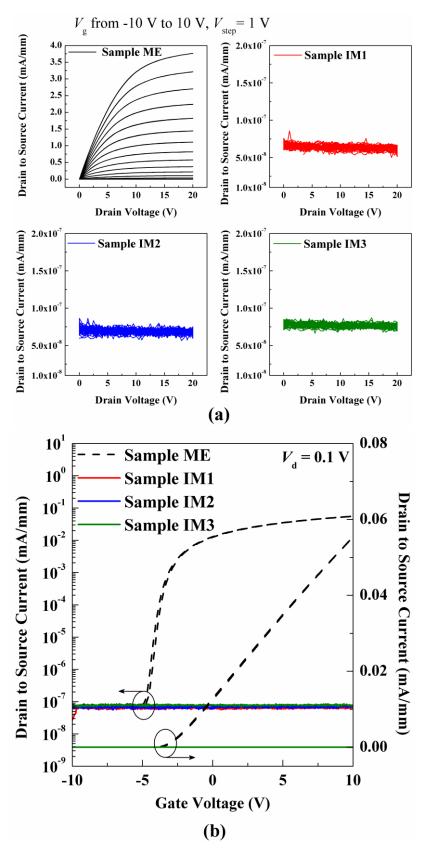

| Figure 4. 12 (a) $I-V$ and (b) transfer characteristics of the circular I-MOSFETs on        | all the samples.        |

|                                                                                             | 69                      |

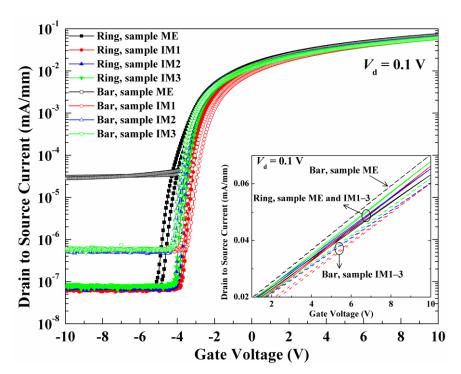

| Figure 4. 13 Transfer characteristics of circular and linear R-MOSFETs on all the           | e samples. 70           |

| Figure 4. 14 Field-effect mobility of R-MOSFETs on all the samples and a circu              | lar I-MOSFET            |

| on sample ME                                                                                | 71                      |

| Figure 4. 15 Breakdown characteristics of the mesa-isolated region and the im-              | planted region          |

| on all the samples.                                                                         | 73                      |

|                                                                                             |                         |

| Table 1. 1 Material properties of GaN and other semiconductor [43]                          | 3                       |

|                                                                                             |                         |

| Table 2. 1 The properties of substrate materials, sapphire, SiC, Si, and GaN                | 17                      |

| Table 2. 2 Characteristics of different implanted dopant in GaN                             | 24                      |

| Table 2. 3 Recess etching process conditions of all the samples                             | 30                      |

| Table 2. 4 The measured maximum field-effect mobility and interface state de-               | nsity of all the        |

| samples                                                                                     | 32                      |

|                                                                                             |                         |

Table 3. 1 List of  $O_2$  plasma and  $O_2$  gas treatment conditions in the PECVD chamber.39

| Table 3. 2 The sheet resistance and ohmic contact resistance measured before a       | nd after O <sub>2</sub> |

|--------------------------------------------------------------------------------------|-------------------------|

| plasma treatment.                                                                    | . 42                    |

| Table 3. 3 Wafer samples used for AlGaN/GaN HFET.                                    | . 50                    |

|                                                                                      |                         |

| Table 4. 1 Measured sheet resistance of isolation region of all the samples          | . 59                    |

| Table 4. 2 The samples with different structures and implant conditions              | . 66                    |

| Table 4. 3 Maximum field-effect mobility and interface state density of the circular | MOSFETs                 |

| on all the samples.                                                                  | . 72                    |

#### **Chapter 1 Introduction**

#### 1.1 Material advantages of GaN

Since the 1950s, after the initial replacement of vacuum tubes by solid-state devices, semiconductor power devices have taken a dominant role with silicon serving as the base material and started the Second Electronic Revolution. However, silicon reached its limitation of physic property after decades of development. Gallium nitride (GaN) as a member of wide band-gap semiconductors has been viewed as a promising candidate to fulfill the requirements of high-frequency, wide bandwidth, high-temperature, and high power in the applications of automobile, wireless communications, military radar.

#### 1.1.1 Material growth and properties

It is widely believed that Johnson et al. [1] first reported on the synthesis of GaN via the reaction of metallic Ga and NH<sub>3</sub> stream in 1932. For early GaN investigations of 1960s and 1970s, only the growth of GaN powder [2-8] and single crystalline GaN needles [9-11] could be achieved, and the popular epitaxial film growth methods were reactive sputtering [12-16], chemical vapor deposition (CVD) [17-22] and reactive molecular beam epitaxy (RMBE) [23]. The first large area GaN was formed on sapphire substrate through the hydride vapor phase epitaxy (VPE) method reported by H.P. Maruska et al in 1969, using flowing HCl vapor over metallic Ga, causing the formation of GaCl which was transported downstream and reacted with NH<sub>3</sub> [24]. However, GaN grown by this approach had large n-type background carrier concentrations, typically  $10^{19}$  cm<sup>-3</sup>. The origin of centers that give rise to background n-type conductivity is conflicting between nitrogen vacancies [25, 26] and residual impurities such as O and Si [27, 28]. Due to the compensation of n-type background carrier, the p-type doping in GaN was difficult. Until 1989, H. Amano et al [29] initially realized p-type conduction with Mg-doped GaN by the low-energy electron-beam irradiation (LEEBI) treatment and the hole concentration was 2×10<sup>16</sup> cm<sup>-3</sup>. In 1991, S. Nakamura et al [30, 31] succeeded in growing ptype GaN using MOCVD.

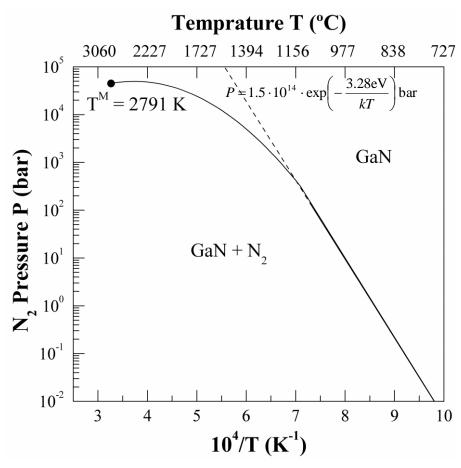

Another difficulty hindered the growth of high-quality GaN film was the lack of substrate material. Although so many years' efforts were expended to grow GaN and develop devices, high-quality, large single crystalline and cost-effective GaN native substrate are now in progress. Crystals are generally grown from liquid phase or gas phase. The challenges to the liquid-phase growth of GaN bulk crystal are 1) the high vapor pressure of N on GaN for melt-grown crystal techniques [32-34], as shown in Figure 1.1; 2) the low solubility of N in the Ga metal melts at

reasonable temperatures and pressures for solution-grown techniques [35-37]. Accordingly, the vapor-phase growth is widely used for epitaxial film growth of GaN due to its inherently slow growth rate.

Figure 1. 1 Equilibrium N<sub>2</sub> pressure over GaN(s) + Ga(l) system based on Ref. [32] and melting points TM from Ref. [34]. The dashed line was calculated for ideal gas [38] and the solid line was fitted with experimental data.

The preference of substrates towards sapphire could be attributed to hexagonal symmetry, simple pre-growth cleaning, and the stability under high concentrations of ammonia and hydrogen at high-temperature. But good epitaxial films could not be obtained due to the lattice mismatch as well as thermal mismatch between the GaN and sapphire until the late 1980s. S. Yoshida et al [23, 39] reported the initially deposition of AlN buffer layer on the sapphire, H. Amano et al [40] and I. Akasaki et al [41] obtained high-quality GaN epitaxial films using AlN buffer layer via metalorganic chemical vapor deposition (MOCVD), S. Nakamura et al [42] first reported the GaN epitaxial film with an n-type background concentration of  $4 \times 10^{16}$  cm<sup>-3</sup>

using the GaN buffer layer. 6H-SiC and Si are also popular substrates: the former has a low lattice mismatch, good electrical conductivity and low film stress; the later has large wafer size, low cost and integration of Si devices. Nowadays, GaN wafers using sapphire, 6H-SiC and Si as substrate have been commercial available, which gives support to the wide range of electronic and optoelectronic applications.

GaN semiconductor has great application potential in high-power and high-frequency electronic devices because of its excellent material properties, such as wide band-gap, high electron saturation velocity, high breakdown field and high electron conductivity of the two-dimensional electron gas (2DEG) in AlGaN/GaN heterostructure. Table 1.1 summarized the material properties of GaN and other semiconductor.

Table 1. 1 Material properties of GaN and other semiconductor [43].

| Material properties                                                              | Si                   | GaAs                | 4H-SiC               | GaN                   | GaN                   |

|----------------------------------------------------------------------------------|----------------------|---------------------|----------------------|-----------------------|-----------------------|

| Crystal structure                                                                | Diamond              | Zincblend<br>e      | Hexagon              | Wurtzite              | Zincblend<br>e        |

| Band-gap $E_{\rm g}$ (eV) 300 K                                                  | 1.12                 | 1.42                | 3.23                 | 3.39                  | 3.2                   |

| Breakdown field $E_{\rm B}$ (MV/cm)                                              | 0.25-0.8             | 0.3-0.9             | 3~5                  | 5                     | 5                     |

| Electron mobility $\mu_n \text{ (cm}^2 \cdot \text{v}^{-1} \cdot \text{s}^{-1})$ | 1450                 | 8000                | ≤900                 | ≤1000                 | ≤1000                 |

| Hole mobility $\mu_p \text{ (cm}^2 \cdot \text{v}^{-1} \cdot \text{s}^{-1})$     | 500                  | 400                 | ≤120                 | ≤200                  | ≤350                  |

| Saturation electron velocity $v_s$ (10 <sup>7</sup> cm/s)                        | 1                    | 0.7                 | 1.9                  | 2.5                   | 2.5                   |

| Thermal conductivity<br>χ (W·cm <sup>-1</sup> ·K <sup>-1</sup> )                 | 1.56                 | 0.46                | 3.7                  | 1.3                   | 1.3                   |

| Intrinsic carrier concentration $n_i$ (cm <sup>-3</sup> ) 300K                   | 9.65×10 <sup>9</sup> | 2.1×10 <sup>6</sup> | 8.2×10 <sup>-9</sup> | 3.85×10 <sup>-1</sup> | 1.04×10 <sup>-8</sup> |

The band-gap of GaN (wurtzite structure) is 3.4 eV, which is three times larger than Si. The wide band-gap gives rise to a low intrinsic carrier concentration, which means GaN devices

need to operate at higher temperature to reach the same intrinsic carrier concentration of Si at room temperature, namely, GaN-based devices can work at harsh temperature environment. GaN-based devices can also work at high voltage because the breakdown field of GaN is much higher than Si and GaAs. The high electron velocity characteristics make GaN devices operate at high frequency as well. In addition, as a direct wide band-gap semiconductor, GaN plays an important role in optoelectronics devices, such as green and short wavelengths emitters and detectors.

#### 1.1.2 Crystal structure

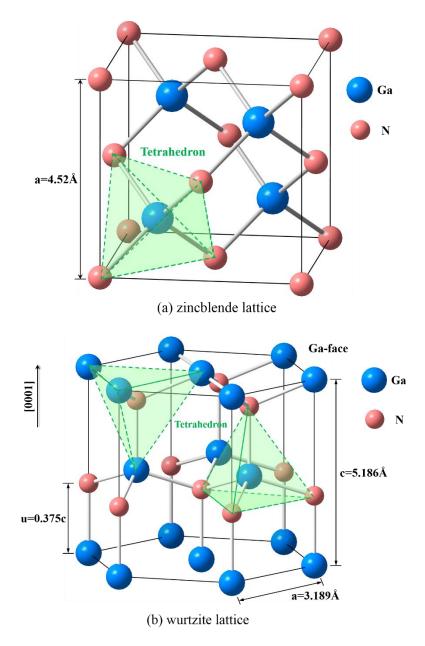

GaN as III-N based semiconductors exist under different crystal structures, wurtzite, zincblende and rock-salt [44]. In general, as ambient conditions, for III-N based semiconductors wurtzite structure is thermodynamically stable; zincblende structure is thermodynamically metastable, while rock-salt structure is formed only under high pressure. GaN films of wurtzite structure have been grown on *c*-orientation substrates which generally transfer their hexagonal symmetry to GaN, such as (0001) sapphire or (0001) 6H-SiC. GaN films of zincblende structure can be stabilized by epitaxial growth on substrates of cubic structure, such as (001) GaAs, (001) 3C-SiC or (001) Si substrate. In this thesis, GaN samples involved in all the experiments are under wurtzite structure.

Both of zincblende and wurtzite structure have tetrahedral coordination: each atom is surrounded by four equidistant nearest neighbors which lie at the corners of a regular tetrahedron. The main difference between these two close-packed structures is the layer stacking sequence: for the zincblende structure, the stacking sequence of (1111) layers is ABCABCABC... along the <111> direction; for the wurtzite structure, the stacking sequence of (0001) layers is ABABAB... along the <0001> direction.

Figure 1.2 shows the wurtzite and zincblende lattice structure of GaN. The zincblende lattice consists of two interpenetrating face-centered cubic (fcc) sub-lattice with the same dimension of lattice constant a=4.52Å [43]. One sub-lattice is gallium and the other is nitrogen, each sub-lattice are shifted against each other along the body diagonal of cubic cell by 1/4 of the width of the unit cell (Figure 1.2 (a)). The wurtzite structure has a hexagonal unit cell and consists of two interpenetrating hexagonal close-packed (hcp) sub-lattice, which constituted by gallium and nitrogen atoms respectively. The wurtzite structure is defined by two lattice constant, a=3.189Å, c=5.186Å, as shown in Figure 1.2 (b). Each sub-lattice are shifted against each other along the c-orientation (i.e. [0001] direction) by the distance u= (3/8) c=0.375c.

Figure 1. 2 Illustration of (a) zincblende lattice and (b) Gallium-face wurtzite lattice of GaN.

#### 1.1.3 Polarization effects and 2DEG

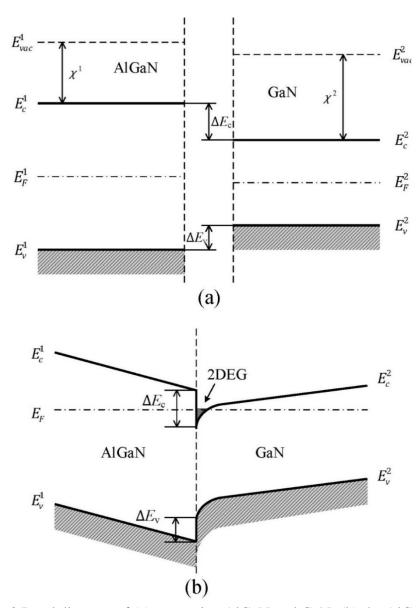

The most unique feature of GaN-based semiconductor is the formation of high density of 2DEG in a quantum well along a heterojunction. The heterojunctions are commonly achieved by the use of alloys, and GaN is commonly alloyed with AlN to form AlGaN. The band-gap and resistivity of Al<sub>x</sub>Ga<sub>1-x</sub>N increase as a function of the Al mole fraction, while the carrier concentration and hall mobility decrease [45]. As shown in Figure 1.3, the band-gap of AlGaN is wider than that of GaN, the carrier accumulation would occur at the interface of AlGaN/GaN heterostructure.

Figure 1. 3 Band diagram of (a) seperating AlGaN and GaN; (b) the AlGaN/GaN heterostructure.

Unlike the 2DEG formation of AlGaAs/GaAs heterostructure, in which the electrons are mainly provided by the dopants in AlGaAs and GaAs. The high density of 2DEG in AlGaN/GaN heterojunction is induced by polarization effects. This sheet density of 2DEG in AlGaN/GaN is up to  $1 \times 10^{13}$  cm<sup>-2</sup> without intentional doping. The polarization effects cause extremely strong electric field within the heterojunction, which would modulate the band structure and make the quantum well of GaN side deep and narrow, and this is benefit to attract and accumulate free electrons into the well.

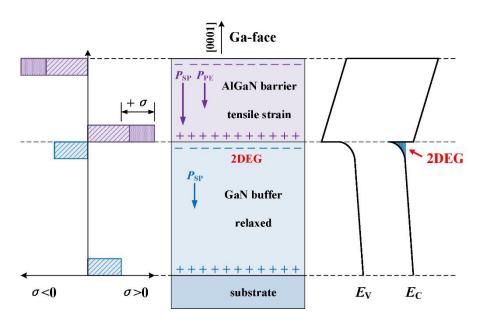

Group III-N based semiconductor exist stronger spontaneous polarization and piezoelectric polarization comparing with other group III-V based semiconductor. Zincblende

group III–V compounds present no spontaneous polarization because lattice structure symmetry counteracts the polarization of covalent bonding. While wurtzite group III–V compounds present a spontaneous polarization along the c-axis direction. Both of structures present piezoelectric polarization. At an abrupt interface of a top/bottom layer heterostructure, the changes of polarization field within a bilayer would induce a sheet charge density  $\sigma$  defined by

$$\sigma = P_{Top} - P_{Bottom} \quad (1.1)$$

where P is polarization intensity [46]. If this sheet charge density is positive ( $+\sigma$ ), free electrons will compensate this charge and form a 2DEG. If the sheet charge density is negative ( $-\sigma$ ), holes would accumulate.

In general, Ga-face polarity is obtained in smooth morphology GaN films grown by MOCVD and N-face polarity is obtained in high-quality GaN films grown by molecular beam epitaxy (MBE). And the polarity of Ga-face wurtzite GaN is opposite to N-face wurtzite GaN, which would alter the sheet charge density's properties of positive or negative. Therefore, for Ga-face AlGaN on top of GaN heterostructure grown pseudo orphic, as shown in Figure 1.4,  $\sigma$  is positive and determined by

$$\sigma = P_{Top} - P_{Bottom} = \left(P_{SP,AlGaN} + P_{PE,AlGaN}\right) - P_{SP,GaN} \quad (1.2)$$

where  $P_{SP}$  and  $P_{PE}$  is intensity of spontaneous polarization and piezoelectric polarization, respectively.

Figure 1. 4 Scheme of sheet charge density, polarization directions and conduction band diagram of Ga-face AlGaN/GaN heterostructures.

#### 1.2 Overview of GaN-based field-effect transistors

GaN-based power transistors can be generally divided into two categories: one is linear device for power amplification at high frequencies such as AlGaN/GaN heterojunction field-effect transistor (HFET); the other is switching power device for electricity conversion such as GaN metal-oxide-semiconductor field-effect transistor (MOSFET). This thesis mainly takes aim at AlGaN/GaN HFET and GaN MOSFET. After more than 20 year's efforts, remarkable progress in development of GaN-based field-effect transistors (FETs) has been achieved.

#### 1. 2. 1 AlGaN/GaN HFET

The AlGaN/GaN HFET is based on AlGaN/GaN heterostructure. The field-effect transistor formed on the AlGaN/GaN heterostructure and using 2DEG as the channel is called AlGaN/GaN high electron mobility transistors (HEMTs). The mobility of AlGaN/GaN HEMTs is enhanced due to the high density of 2DEG, and up to 2000 cm<sup>2</sup>·v<sup>-1</sup>·s<sup>-1</sup> [47]. AlGaN/GaN HEMT with impressive tradeoff between specific on-resistance and breakdown voltage is regarded as one of the prospective candidates for the next generation of microwave power devices.

In 1993, M. A. Khan et al fabricated the first GaN metal semiconductor field-effect transistor (MESFET) with a gate length of 4 µm and a maximum transconductance of 23 mS/mm at gate voltage of -1 V [48]. Subsequently, they reported the first fabrication of HEMT based on AlGaN/GaN heterojunction with a transconductance of 28 mS/mm at 300 K [49]. By means of a new ohmic contact using Ti/Al reported by M.E. Lin et al [50], several kinds of device structures were proposed. A. Ozgur et al fabricated GaN modulation-doped FETs (MODFETs) with a transconductance of 120 mS/mm and a 300 mA/mm current at gate bias of 3 V [51]. M.A. Khan et al fabricated doped-channel HFETs (DC-HFETs) with a gate length of 0.25 µm and obtained a cutoff frequency of 70.8 GHz [52]. In this period, the major obstacle to device improvement was poor crystal quality and poor thermal environment. Not until high-quality GaN films epitaxially grown on SiC substrate succeeded did the device fabrication technology for GaN-based FET start being mature. Y. F. Wu et al reported the first radio frequency (RF) power performance, which was a power density of 1.1 W/mm at 2 GHz with a power added efficiency (PAE) of 18.6% for 1 µm gate-length GaN MODFET [53].

Two important techniques had driven the progress in GaN-based power performance: first was the introduction of a SiN passivation layer [54], which had an effect on suppression of the current collapse and improving the output power density [55]; second was the adoption of field-

plate structures [56], which could both increase the breakdown voltage and reduce the current collapse effect, improving the power performance. In 2004, Y. F. Wu et al reported a continuous wave output power density of 32.2 W/mm and PAE of 54.8% at 4 GHz at gate bias of 120 V [57]. In 2008, Moon et al reported GaN HEMT with n<sup>+</sup> source ledges was fabricated and a PAE of 55% at 5 W/mm at 33 and 36 GHz was achieved [58]. To date, multiple companies announce commercial product of GaN HEMT devices with outstanding performance, including TriQuint, Cree, RFMD, Eudyna, and so on [59].

However, some critical issues still restrain the inherent high performance of AlGaN/GaN HFETs for practical application. One of these issues is the large leakage current along the isolation region, which causes off-state power loss, additional noise, and reliability problems. An effective electrical isolation around the active area is thus essential to achieve low off-state drain current.

#### 1. 2. 2 GaN MOSFET

The breakdown characteristics of AlGaN/GaN HEMTs were limited by the large leakage current of Schottky gate. To reduce the gate leakage current and improve the breakdown voltage, F. Ren et al reported the first MOS gate using a  $Ga_2O_3$  ( $Gd_2O_3$ ) film [60]. M. A. Khan et al reported a  $SiO_2$ /AlGaN/GaN MOS-HFET and the gate leakage current reduced by six orders of magnitude than AlGaN/GaN HFET [61], and low gate leakage current was beneficial to improve low-frequency noise [62]. P. D. Ye et al reported atomic-layer-deposited (ALD)  $Al_2O_3$  as the gate oxide for GaN MOS-HFET [63]. N.-Q. Zhang et al reported high voltage GaN MOS-HFET with an on-resistance of 1.7 m $\Omega$ ·cm<sup>2</sup> and breakdown voltage of 1.3 kV [64].

Another critical issue for GaN-based FETs is normally-on operation. For power operation, normally-off operation is necessary to achieve safe operation and low power consumption. Y. Cai et al reported enhancement mode (E-mode) AlGaN/GaN HEMT with a threshold voltage of 0.9 V using fluoride-based plasma treatment on the gate region [65]. Some groups reported a recessed-gate structure forming by the selective reduction of 2DEG layer only under gate metal in AlGaN/GaN HEMT [66, 67]. The resistance from gate to channel was reduced by this structure and the threshold voltage could be controlled by the recess depth. Combining the advantages of MOS channel with recessed-gate, a recessed MOS-gate AlGaN/GaN HFET was proposed, previously called hybrid MOS-HEMT or MOS Channel-HEMT (MOSC-HEMT) [47]. The 2DEG layer under the gate region is completely removed and the channel is controlled by the MOS gate, this device called as GaN MOSFET. T. Oka et al reported an AlGaN/GaN MOSFET with a threshold voltage of 5.2 V and a maximum field-effect mobility of 120

cm<sup>2</sup>·v<sup>-1</sup>·s<sup>-1</sup> using SiN film [68]. H. Kambayashi et al reported normally-off AlGaN/GaN MOSFET with the threshold voltage of 3.7 V [69]. K.-S. Im et al reported AlGaN/GaN MOSFET with an  $Al_2O_3$  gate oxide and a maximum field-effect mobility of 225 cm<sup>2</sup>·v<sup>-1</sup>·s<sup>-1</sup> [70].

GaN MOSFET have potential use for power integrated circuits (ICs) owing to its lateral structure. Not only device isolation but also field isolation is necessary for development of GaN MOSFET power ICs. However, little work of device isolation techniques has been performed. Thus, as one of key challenges, device isolation is necessary for GaN-based FETs.

#### 1. 3 Significance of device isolation

Device isolation, meaning electrical isolation between devices, is an ability of technology to make each device operate independently and get rid of the influence of proximity devices. Device isolation is one of the primary process steps and significantly important for the high-voltage operation of GaN-based FET and for GaN ICs. In silicon IC technologies, three most commonly adopted isolation methods are junction isolation, local oxidation of silicon (LOCOS), and trench isolation [71].

Nevertheless, these methods are difficult to be adopted for GaN MOSFETs using the recent GaN technologies. The native oxide forming by thermal oxidation can achieve thick oxide on silicon, but for now it is not available to natively grow thick gallium oxide (Ga<sub>2</sub>O<sub>3</sub>) on GaN by thermal oxidation. The largest thickness of silicon oxide (SiO<sub>2</sub>) forming by chemical vapor deposition (CVD) is usually limited, because the oxide film is easy to crack when thickness becomes large due to different thermal expansion coefficients between GaN and SiO<sub>2</sub>. Moreover, it is difficult to obtain highly-doped p-GaN layer by selective ion implantation. For the reasons above, GaN MOSFETs are still developed on i-GaN or p-GaN layer without any field isolation structure.

#### 1. 3. 1 Device isolation of AlGaN/GaN HFET

Currently, mesa isolation as the simplest technique is widely adopted for AlGaN/GaN HFETs through dry etching to remove the 2DEG layer around active region [72, 73]. However, the etching damage was introduced due to the plasma bombardment of the mesa surface during dry etching process, particularly nitrogen vacancy, which acts as donor-like defect and leads to high surface leakage current. The large leakage current causes off-state power loss, additional noise, and reliability problems. The mesa structure is commonly formed by Cl<sub>2</sub>-based dry

etching process (Figure 1.5a), and the gas sources are Cl<sub>2</sub>, SiCl<sub>4</sub>, BCl<sub>3</sub>/Cl<sub>2</sub>, and so on [74-76]. To reduce the surface leakage current on the mesa-isolated region, dielectrics filling like Si<sub>3</sub>N<sub>4</sub>, SiO<sub>2</sub>, and Sc<sub>2</sub>O<sub>3</sub> were used [77-79]. Some groups employed surface treatment such as N<sub>2</sub>/H<sub>2</sub> treatment, UV ozone, and O<sub>2</sub> plasma to eliminate etching damage and reduce leakage current [78, 80]. The fabrication process steps of dielectrics deposition and lithography are added for these two methods.

Figure 1. 5 Schematic cross-section of (a) mesa structure and (b) ion implantation in AlGaN/GaN heterojunction.

For compound semiconductors, ion implantation, in addition to forming doped region, can also achieve device isolation through producing deep-level traps or recombination centers to form the high resistivity region. Implantation isolation offers the advantage of maintaining planar device morphology. Several ion species have been employed in GaN material or AlGaN/GaN HFETs, such as H<sup>+</sup>, He<sup>+</sup>, N<sup>+</sup>, P<sup>+</sup>/He<sup>+</sup>, Zn<sup>+</sup>, O<sup>+</sup>, Fe<sup>+</sup> ions [81-88]. As shown in Figure 1.5b, ion implantation is usually used by eliminating the 2DEG in AlGaN/GaN heterojunction.

#### 1. 3. 2 Field isolation of MOSFET

The isolation technologies in the Si MOSFET ICs is different from ordinary FETs, because a reverse channel appears beneath an field oxide since that an interconnection wire on the top of the field oxide can probably behave as a parasitic MOSFET-like device, as shown in Figure 1.6a. In order to prevent the formation of the reverse channel, field oxidation and field implantation (Figure 1.6b) are normally used to increase the threshold voltage according to

$$V_{T} = \phi_{ms} - \frac{Q_{f} + Q_{B}}{C_{ox}} + 2\psi_{B}$$

(1.3)

The field region can be non-conductive even under high voltage and field isolation succeeds. Hence, field isolation is also indispensable for GaN MOSFET ICs.

Figure 1. 6 Schematic of (a) the parasitic MOSFET-like device in Si MOSFET ICs [89]; (b) field implantation and LOCOS isolation [71].

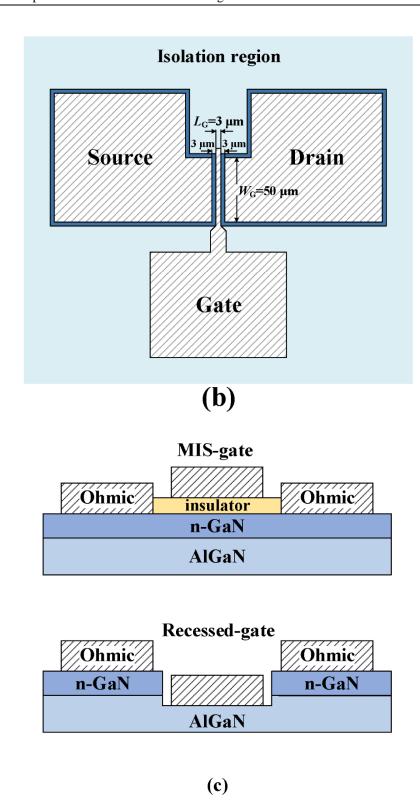

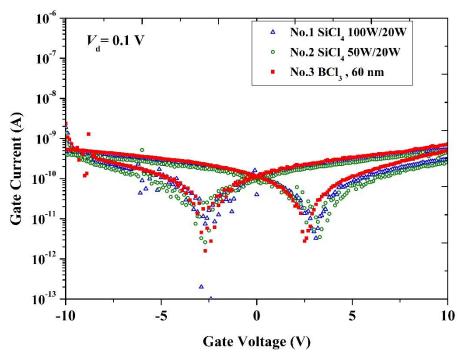

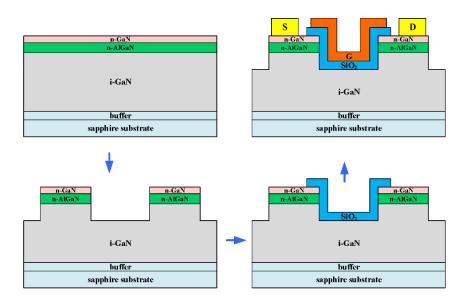

Similar to AlGaN/GaN HFET, the mesa structure is also simply adopted in many reports to achieve device isolation for the GaN MOSFETs. Unfortunately, in our previous work, we have found a phenomenon of parallel channel in a long-channel linear MOSFET (Figure 1.7a) if only mesa isolation was adopted. As shown in Figure 1.8, an overestimated maximum

mobility and off-state drain current of the linear device was about 192 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> and 10<sup>-3</sup> mA/mm, while for a long-channel circular device (Figure 1.7b) with the same recess and mesa condition it was about 150 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> and 10<sup>-8</sup> mA/mm, respectively. Besides this mobility discrepancy, two-step drain current and mobility were also appeared in the gate voltage range of around -4 V. The reason is considered that, a parasitic device could appear on the isolation region of a linear GaN MOSFET if a MOS-like structure is formed. Because the etching bias of the mesa process was higher than that of the recess process, leading to a greater plasma-induced damage on etching surface, and thus a negatively-shifted threshold voltage and relatively low mobility. As a result, the actual channel width is larger than the designed width and the field-effect mobility calculated from the transfer characteristics with the designed channel width will be overestimated. Therefore, it is necessary to develop effective field isolation methods for GaN MOSFETs and integrated circuits based on GaN MOSFETs in the future.

Figure 1. 7 Schematic of (a) a long-channel linear and (b) a long-channel circular GaN MOSFET on AlGaN/GaN heterostructure.

Figure 1. 8 Transfer characteristics and field-effect electron mobility of a circular and a linear MOSFET. Both of devices were in the same recess condition and with only mesa isolation.

#### 1. 4 Motivation and objectives

#### 1. Motivation

For AlGaN/GaN HFET, the large leakage current of Schottky gate and current collapse effect have been attractive for a long time, and lots of investigations were reported. However, several work was focused on the leakage current caused by mesa etching damage, For example, dielectrics filling and surface treatment have been employed to eliminate etching damage and reduce leakage current. In these processes, O<sub>2</sub> plasma treatment is relatively easy and feasible because dielectrics deposition or lithography step is not needed and O<sub>2</sub> plasma can be generated by a plasma-enhanced chemical vapor deposition (PECVD) system. The oxidation mechanism of O<sub>2</sub> plasma treatment is not clear yet. Therefore, we studied the influence of O<sub>2</sub> plasma treatment on the mesa-isolated region of AlGaN/GaN HFETs by using the PECVD system, an effective treatment condition was established, and oxidation mechanism of O<sub>2</sub> plasma treatment were analyzed. Finally, AlGaN/GaN HFETs were fabricated with O<sub>2</sub> plasma treatment on the isolation region and characterized thereafter.

For GaN MOSFET, an ineffective isolation method like mesa structure would cause a parasitic MOSFET in the isolation region of linear device. Therefore, not only device isolation but also field isolation should be considered for GaN MOSFET. Ion implantation is a good option as device isolation method for compound semiconductor. However, the influence of thermal stability caused by annealing processes should also be considered. Therefore, the boron ion implantation for GaN MOSFET was used to prevent the formation of parasitic MOSFET in the isolation region. Circular and linear MOSFET was fabricated and compared to evaluate the isolation effectiveness. Moreover, the process sequences of annealing processes and implantation were altered to improve the resistivity of implanted-region.

#### 2. Objectives

This thesis investigates the device isolation technologies for GaN-based FETs to overcome the disadvantages of mesa isolation. For AlGaN/GaN HFET, a process of O<sub>2</sub> plasma was employed on the mesa-isolated region to eliminate dry etching damage and reduce the leakage current; an effective treatment condition was established; oxidation mechanism of GaN surface treated by O<sub>2</sub> plasma were analyzed; the isolation effectiveness of AlGaN/GaN HFET with O<sub>2</sub> plasma treatment was evaluated. For GaN MOSFET, a process of boron ion implantation was adopted to prevent the formation of parasitic MOSFET in the isolation region and achieve field isolation; the implantation profile of boron ions and the sheet resistance of implanted region were described; the processes of annealing and ion implantation were improved; Circular and

linear MOSFETs were fabricated and characterized to evaluate the isolation effectiveness.

#### 1. 5 Outline of dissertation

This thesis is divided into five parts.

In chapter 1, the advantages of GaN material and GaN-based device and the significance of device isolation and field isolation were introduced.

In chapter 2, the basic structure and fabrication processes, test methods and evaluation technology for AlGaN/GaN HFET and GaN MOSFETs were described in details. The basic fabrication processes included cleaning, mesa etching, ohmic contact, gate contact, recess etching (for GaN MOSFET), and gate oxide deposition (for GaN MOSFET). The current-voltage (*I*–*V*) and capacitance-voltage (*C*–*V*) measurements were conducted for AlGaN/GaN HFET and GaN MOSFETs and the transmission line model (TLM) and MOSFET structures were used to evaluate the isolation effectiveness. Circular and linear GaN MOSFETs were fabricated to examine the existence of a parasitic MOSFET-like device and evaluate the effectiveness of the isolation process, *I*–*V* and *C*–*V* characteristics were measured and the field-effect electron mobility could be calculated by a method of gate capacitance-transconductance and interface state density could be calculated using oxide capacitance and *I*–*V* characteristics.

In chapter 3, the influence of O<sub>2</sub> plasma treatment on the mesa-isolated region of AlGaN/GaN HFETs was studied. The effective condition was established by *I*–*V* characteristics, and the *I*–*V* results indicated that isolation current were strongly dependent on treatment temperature. The defect levels and chemical properties of the treated GaN surface were characterized through photoluminescence (PL) spectrum and X-ray photoelectron spectroscopy (XPS). AlGaN/GaN HFETs were fabricated with O<sub>2</sub> plasma treatment and characterized.

In chapter 4, GaN MOSFETs using boron ion implantation as field isolation process were fabricated and the effectiveness of boron field implantation was evaluated. The process of boron field implantation was developed and improved for GaN MOSFETs, the elimination of parasitic MOSFETs was confirmed by the I-V characteristics of circular MOSFETs fabricated in the isolation regions, and the isolation effectiveness of process was evaluated through the comparison of I-V characteristics between circular and linear device. The influence of implantation damage on device performance for different isolation structures were evaluated by the calculation of the field-effect electron mobility and the density of interface traps ( $D_{\rm it}$ ) according to I-V and C-V tests.

In chapter 5, the results are summarized and the future work is proposed.

## Chapter 2 Fabrication process, test methods and evaluation technology of GaN-based FET

#### 2. 1 AlGaN/GaN HFET

The ability of the generation of 2DEG layer by heterostructure is the most noteworthy advantage which distinguished GaN from other semiconductors. The AlGaN/GaN HFET is based on AlGaN/GaN heterostructure and used the 2DEG layer as a channel.

As mentioned above, the success of GaN epitaxial process is attributed to the viability of heteroepitaxy. There are three substrates that have been utilized to achieve commercial success with heteroepitaxial GaN-based devices: sapphire, SiC and Si. Table 2.1 compares the properties of sapphire, SiC, Si, and GaN.

Table 2. 1 The properties of substrate materials, sapphire, SiC, Si, and GaN.

| Properties                      | Sapphire          | 6H-SiC           | Si            | GaN       |

|---------------------------------|-------------------|------------------|---------------|-----------|

| Mismatch of lattice (%)         | 14                | 3.5              | 17            | _         |

| Thermal conductivity (relative) | 0.4               | 4.9              | 1.56          | 1.3       |

| Electrical Resistivity (Ω·cm)   | >10 <sup>14</sup> | >10 <sup>5</sup> | $10^4 - 10^5$ | $>10^{5}$ |

| Thermal stability               | Very high         | Very high        | Moderate      | _         |

| Band-gap $E_{\rm g}$ (eV) 300 K | 9.9               | 3.0              | 1.2           | 3.39      |

| Substrate size (inch)           | 6                 | 6                | 8-12          | 2         |

| Substrate cost (relative)       | High              | Very high        | low           | Very high |

| Compatibility with ICs          | Low               | Moderate         | Very high     | _         |

6H-SiC substrate has a lowest lattice mismatch and highest thermal conductivity, and is the best candidate for GaN heteroepitaxy growth in spite of the highest product cost. Sapphire substrate has highly thermal stability and a relative lower lattice mismatch, and is able to cut off the channel of GaN MOSFET due to the high resistivity. Silicon substrate is benefit for batch handling of integrated products due to the highest compatibility, lowest product cost, and largest substrate size. Therefore, tradeoffs must be considered for academic research, sapphire and silicon substrate are commonly used in our experiments.

Another crucial problem for AlGaN/GaN heterostructure is the current collapse effect by

the electron injection at the source and drain surface [90, 91]. Current collapse is a charging up of a second virtual gate appearing in the gate drain access region, which could modulate the 2DEG and finally make the device show strong hysteresis [92]. A n-type GaN cap layer with high doping density could be used to eliminate the current collapse effect [93]. Moreover, the use of n-GaN cap layer can not only eliminate the current collapse effect but also heal surface inhomogeneities and lower the ohmic contact resistance.

#### 2. 1. 1 Structures of AlGaN/GaN HFET

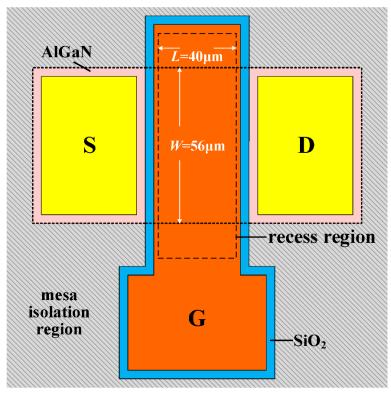

A conventional linear AlGaN/GaN HFET with mesa isolation is shown in Figure 2.1a. The gate length  $L_{\rm G}$  of the device is 3  $\mu$ m, the gate width  $W_{\rm G}$  is 50  $\mu$ m, and the spacing between source/drain electrode and gate electrode is 3  $\mu$ m (Figure 2.1b). There are several different gate structures like MIS-gate, recessed-gate (Figure 2.1c), the ordinary Schottky gate without thinning AlGaN layer was used because the whole attention is centered on the isolation region.

Figure 2. 1 The cross section (a) and bird view (b) of a linear AlGaN/GaN HFET with mesa isolation. (c) shows MIS-gate and recessed-gate structures.

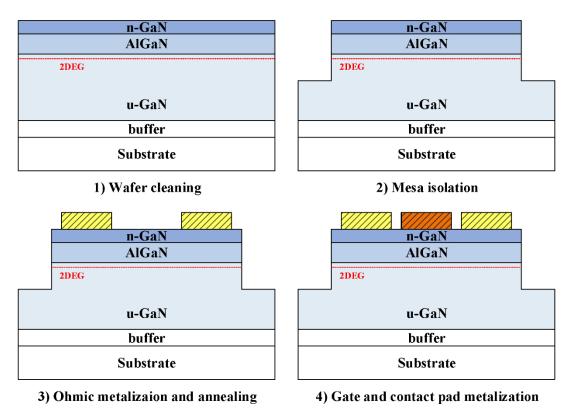

#### 2. 1. 2 Fabrication process of AlGaN/GaN HFET

Borrowing from GaAs p-HEMT technology, conventional AlGaN/GaN HFET processing schemes often proceed through a sequence of 1) wafer cleaning, 2) mesa isolation, 3) ohmic metalization and annealling, 4) gate and contact pad metalization, and 5) passivation, as shown in Figure 2.2. The process of passivation was not under our consideration because the gate region and isolation region were passivated by dielectric film simultaneously, which has an obvious influence on the isolation effectiveness evaluation.

Figure 2. 2 The fabrication process of AlGaN/GaN HFET with mesa isolation.

The detailed instruction of each process will be introduced.

#### 1) Wafer cleaning

The wafer was cleaning with SPM ( $H_2SO_4$ : $H_2O_2 = 4$ :1, volume ratio) solution and organic solution in sequence. The wafer was dipped in SPM solution heating at 100 °C for 10 min, cleaned with deionized (DI) water and blow-dry using nitrogen gun. Then the wafer immersed in the acetone solution was cleaned with ultrasonic cleaner for a few minutes. Finally, the wafer was rinsed with acetone, methanol, and DI water.

#### 2) Mesa isolation.

A mesa structure is formed through dry etching. Dry etching techniques for III–V nitrides includes chemically assisted ion beam etching, laser ablation, reactive ion beam (RIE) etching, and inductively coupled plasma (ICP) etching. At present, inductively-coupled chlorine-based plasmas have become the most common method to etch GaN due to high high-density plasma and high uniformity over large areas, lower ion bombardment energy relative to RIE, and lack of electromagnets and waveguides required for electron cyclotron resonance (ECR).

In our experiments, an ICP system–RIE-200-iPG (from SAMCO, Inc., Fushimi, Kyoto, Japan) was employed with a SiCl<sub>4</sub> source and a Cl<sub>2</sub> source. Figure 2.3 shows the internal components of the equipment. Inductively coupled coils generates plasma and the plasma density is controlled by ICP power. The bias power controlled the speed that plasma move towards sample, a higher bias power means a stronger ion bombardment on the sample. A helium gas was used for cooling to keep the sample stage at room temperature during the etching process.

Figure 2. 3 Schematic of internal components in the ICP system.

In our previous work [94, 95], a two-step etching process was used for mesa formation. The first step was done by SiCl<sub>4</sub> gas with a flow rate of 4 sccm, ICP power of 50 W, bias power of 100 W and at a working chamber pressure of 0.25 Pa. The second step was done by Cl<sub>2</sub> gas with a flow rate of 4 sccm, ICP power of 50 W, bias power of 50 W and at a working chamber

pressure of 0.25 Pa. The second etching of Cl<sub>2</sub> gas was planned to remove any possible oxide induced by SiCl<sub>4</sub> gas. However, it was found that much more damage was produced by Cl<sub>2</sub> etching, and the details will be discussed in Chapter 3.

Afterwards, the mesa etching condition was altered to be same with the recess etching condition used for MOSFET. And this recess condition was SiCl<sub>4</sub> gas flow of 3 sccm, ICP power of 100 W, bias power of 20 W, and working chamber pressure of 0.25 Pa. The etching rate under this condition was approximately 1.25 nm/min [96].

Usually, a 2 µm positive photoresist (abbreviated as PR, HPR-1183L, Fujifilm Corp., Minato, Tokyo, Japan) layer was used as the etching mask. The mesa depth was approximately 100 nm, in which a good-quality GaN surface could be obtained. After dry etching, a HNO<sub>3</sub>:HF buffered solution (BHF; 1:1, volume ratio) was used to remove possible Si contaminants on the etched surface and good for reduction of surface current on the mesa-isolated region.

#### 3) Ohmic metallization and annealing.

Most GaN ohmic contact was achieved using multilayers of Ti/Al/x/Au, where x may be Ti, Ni, Pt, Mo, or Pd. Each kind of metal play different roles during the formation of ohmic contact, and their roles are not well agreed yet. One issue unique to GaN ohmic contact formation is the extremely high annealing temperature, typically 850 °C, which is beyond the melting point of Al (661°C) and leading to rough ohmic contact morphology.

Figure 2. 4 Pictures of (a) before 850 °C annealing and (b) after 850 °C annealing.

A metal stack of Ti/Al/Ti/Au (50/200/40/40 nm) was deposited as ohmic electrodes through sputtering (ALVAC MNS-2000-RF-HS). After deposition, the extra metal layer was removed by a lift-off process and annealed at 850 °C for 1 min in nitrogen ambient. The ohmic

the contact resistance was usually 0.1–1  $\Omega$ ·mm.

#### 4) Gate and contact pad metallization.

Traditionally, most AlGaN/GaN HFET have employed Ni/Au as the Schottky gate contact due to good electrical properties and adhesion to the (Al)GaN surface. However, other candidates for gate electrode have been proposed, such as Pt/Au, TiN/W/Au [73, 97], a Ni/Au (70/30 nm) bi-layer was deposited as the gate metal in out experiments. The annealing is not needed for gate contact formation. Figure 2.5 shows a picture of AlGaN/GaN HFETs after finishing the gate metallization.

Figure 2. 5 The picture of AlGaN/GaN HFETs after finishing the gate metallization.

#### 2. 1. 3 Test methods of AlGaN/GaN HFET

The AlGaN/GaN HFET are characterized by I-V measurement with semiconductor parameter analyzer (Agilent HP 4155C). The I-V characteristics of TLM test can extract the ohmic contact resistance and sheet resistance. The I-V test on the DC performance of AlGaN/GaN HFET includes gate current-gate voltage ( $I_g-V_g$ ), drain current-drain voltage ( $I_d-V_d$ ), and drain current-gate voltage ( $I_d-V_g$ ). Transconductance  $G_m$  as an important parameter reflects the controlling ability of Schottky gate upon the channel current, and equals to the derivatives of  $I_d-V_g$  characteristics. The breakdown characteristics of TLM structure were conducted using I-V test.

#### 2. 2 GaN MOSFET

GaN MOSFET can realize E-mode operation which is unable for AlGaN/GaN HFET. Four key factors are necessary to realize a good MOSFET:1) a good oxide layer with very low leakage current; 2) a good channel controlled by the gate bias to realize on and off state; 3) a good source and drain ohmic contacts to provide carriers and connecting the MOS channel; 4) a good interface between the oxide layer and substrate semiconductor with low interface state intensity.

In an ordinary Si n-MOSFET, the drain and source regions are formed through the heavily n-type doping in the P-type substrate, and gate oxide SiO<sub>2</sub> is formed by thermally oxidation, as shown in Figure 1.6a. Although some groups realized GaN MOSFET using this structure [98-100], it is still difficult to complicate with Si technology. Actually, consistent p-type doing in GaN is still the unresolved particular problem. The reasons for this difficulty are: 1) the native n-type background conductivity of GaN; 2) residual implant damage also has n-type character in GaN; 3) lots of nitrogen vacancies on the surface layer leading to a n-type surface. Table 2.2 summarized characteristics of different implanted dopant in GaN.

Table 2. 2 Characteristics of different implanted dopant in GaN.

|          | Max achievable doping level | Ionization level |

|----------|-----------------------------|------------------|

|          | $cm^{-3}$ )                 | (meV)            |

| Donor    |                             |                  |

| Si       | $5 \times 10^{20}$          | 28               |

| S        | $5 \times 10^{18}$          | 48               |

| Se       | $2 \times 10^{18}$          |                  |

| Te       | $1 \times 10^{18}$          | 50               |

| O        | $3 \times 10^{18}$          | 30               |

| Acceptor |                             |                  |

| Mg       | $5 \times 10^{18}$          | 170              |

| Ca       | $5 \times 10^{18}$          | 165              |

| Be       | $5 \times 10^{17}$          |                  |

| С        | n-type                      |                  |

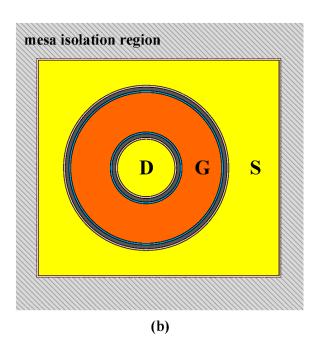

#### 2. 2. 1 Structures of GaN MOSFET

To replace the ion implantation structure, the 2DEG layer in the AlGaN/GaN heterojunction as drain and source, and recessed-gate structure are proposed, as shown in Figure 2.6. The 2DEG layer under gate contact is removed by dry etching, and a recess structure is formed, so this device is called as recessed-gate MOSFET. The remained 2DEG layer as source and drain provides high-intensity electrons, and the channel is formed on the u-GaN layer. To obtain a good coverage of the oxide on the sidewall, the gate recess depth should not be deep. The oxide thickness is usually smaller than 100 nm, hence, the gate recess depth is commonly around 50 nm considering the thickness of 2DEG layer.

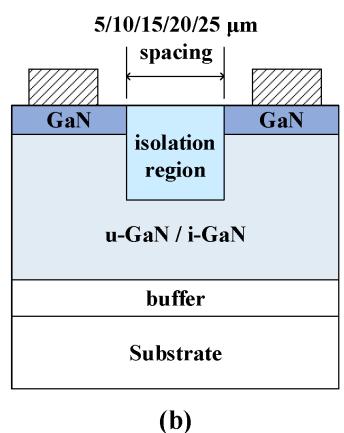

Figure 2. 6 Schematic of recessed-gate structure for GaN MOSFET with mesa isolation.

To avoid the short channel effect only long-channel MOSFET was fabricated, because the parasitic resistance can be ignored due to the large channel resistance. Both of circular and linear MOSFET were fabricated, as shown in Figure 2.7. The linear device has a gate length of 40  $\mu$ m and gate width of 56  $\mu$ m, respectively. The inner radius and the outer radius of the circular are 89  $\mu$ m and 193  $\mu$ m, respectively. The effective channel width W of 819  $\mu$ m which was calculated from

$$W = \frac{2\pi L}{\ln r_{out} - \ln r_{in}} \quad (2.1)$$

where  $r_{\text{out}}$  and  $r_{\text{in}}$  is the outer and inner radius.

**Bar-type MOSFET**

**Ring-type MOSFET**

Figure 2. 7 Schematic of long-channel linear and circular GaN MOSFET.

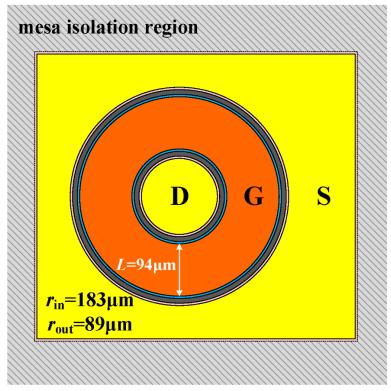

# 2. 2. 2 Fabrication process of GaN MOSFET

The fabrication processes of GaN MOSFET are more complicated than AlGaN HFET. The fabrication process of an ordinary recessed-gate GaN MOSFET contains 1) wafer cleaning, 2) mark etching, 3) mesa isolation, 4) gate recess etching, 5) gate oxide deposition, 6) ohmic metallization and annealing, and 7) gate metallization as shown in Figure 2.8. The processes of gate recess etching and gate oxide deposition will be discussed.

Figure 2. 8 The fabrication process of recessed-gate GaN MOSFET.

#### 1) Gate recess etching

The gate recess was also formed by the same ICP system—RIE-200-iPG with a SiCl<sub>4</sub> source. The etching condition was SiCl<sub>4</sub> gas flow of 3 sccm, ICP power of 100 W, bias power of 20 W, and working chamber pressure of 0.25 Pa. The etching rate under this condition was approximately 1.25 nm/min. However, despite the extremely low etching rate, dry etch-induced lattice damage can severely degrade device performance. The avoidance of etching damage is required to obtain a high-quality channel with high carrier mobility and low interface states. Low ICP and bias power of ICP system could decrease the etching rate which is benefit to reduce etching damage. Low power might also get an irregular recess profile and even failure in the MOSFETs operation.

Etching mask is important for good etching profile. For easy fabrication, PR mask was often used to protect active region during the mesa etching. However, it was found that trenching effect at the bottom near the sidewall was observed if PR mask was adopted, and the SiO<sub>2</sub> as etching mask can improve the recess profile [101]. Therefore, The SiO<sub>2</sub> film of about 500 nm thickness deposited by tetraethylorthosilicate (TEOS) PECVD was used as the recess etching mask. After etching, the BHF solution and HNO<sub>3</sub>: BHF = 1:1 solution were used to remove SiO<sub>2</sub> film and possible contamination of Si on the etched surface.

## 2) Gate oxide deposition

The types and oxidation methods of gate oxide also have an effect on device performance, especially mobility. The common SiO<sub>2</sub> film growth method is PECVD growth using silane- or TEOS-based source. The SiO<sub>2</sub> film deposited with silane-based PECVD was preferred to the film deposited with TEOS source because of a lower interface state intensity. The thickness of gate oxide was controlled under 100 nm. After deposition, a post-annealing process of 1000 °C for 10 min in N<sub>2</sub> ambient would be performed.

The summary of key points of GaN MOSFET fabrication process is as follows. 1) To obtain an etched surface with less damge, a condition of low etching rate and SiO<sub>2</sub> mask are preferred, as well as the use of HNO<sub>3</sub>: BHF = 1:1 solution to clean the etched surface; 2) Silane-based SiO<sub>2</sub> film is prior to TEOS-based film.

#### 2. 2. 3 Test methods of GaN MOSFET

The GaN MOSFET are characterized by I-V measurement with semiconductor parameter analyzer (Agilent HP 4155C), and C-V measurement with LCR meter (Agilent 4284A). The I-V characteristics of TLM test can extract the ohmic contact resistance and sheet resistance. The I-V test on the DC performance of GaN MOSFET includes gate current-gate voltage ( $I_g-V_g$ ), drain current-drain voltage ( $I_d-V_d$ ), and drain current-gate voltage ( $I_d-V_g$ ). Transconductance  $G_m$  as an important parameter reflects the ability of the gate oxide controlling the channel current, and equals to the derivatives of  $I_d-V_g$  characteristics. The frequency of C-V measurement is determined by capacitance-frequency (C-f) measurement, 100 kHz with a signal level of 25 mV.

The gate capacitance-transconductance method was adopted to determine the electron field-effect mobility. According to the basis of the gradual channel approximation of MOSFETs, field-effect mobility could be calculated as

$$\mu_{FE} = \frac{G_M L}{C_{OX} W V_d} \quad (2.2)$$

where L is the gate length,  $C_{OX}$  is the oxide capacitance per unit area, and  $G_{M}$  is the transconductance.

The equivalent circuit of the MOS structure can be presented as the oxide capacitance  $C_{\rm OX}$  connected in series with a parallel connection of the depletion capacitance  $C_{\rm D}$  and the interface-related capacitance  $C_{\rm it}$ . In this case, based on the definition, the subthreshold swing S could be expressed as

$$S = \frac{dV_g}{d \log I_{ds}} = \left(\ln 10\right) \left(\frac{kT}{q}\right) \left(1 + \frac{C_D}{C_{OX}} + \frac{C_{it}}{C_{OX}}\right)$$

(2.3)

where k is the Boltzmann constant, T is the absolute temperature, and q is the electron charge.

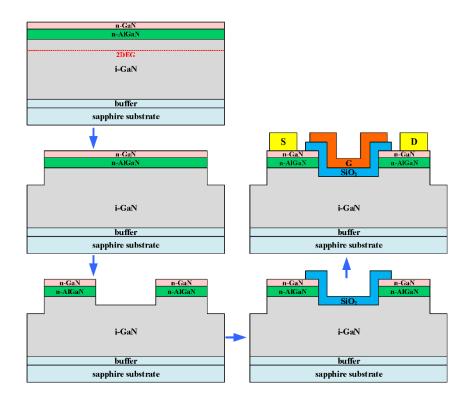

#### 2. 2. 4 Fabrication of GaN MOSFET using BCl<sub>3</sub> etching gas

In our previous work, we achieved a precise control of ICP etching rate of 1.2 nm/min and determined the optimum ICP condition of GaN MOSFETs on AlGaN/GaN heterostructure with the etching gas of SiCl<sub>4</sub>. However, the devices etched with SiCl<sub>4</sub> gas had a negative threshold voltage, the possible reason may be silicon (Si) contamination. Therefore, we tried to use BCl<sub>3</sub> instead of SiCl<sub>4</sub> as the gate recess etching gas in order to reduce the influence of Si contamination on threshold voltage.

The GaN MOSFETs on AlGaN/GaN hetero-structure with different recess etching conditions was fabricated and characterized. The device fabrication process was based upon standard photolithography and lift-off technologies. The gate recess was conducted utilizing ICP system with BCl<sub>3</sub> and SiCl<sub>4</sub> gas. The SiO<sub>2</sub> film of about 500 nm thickness deposited by tetraethylorthosilicate (TEOS) PECVD was used as the etching mask. The etching conditions of three samples are listed in Table 2.3.

Sample No. 1 and No. 2 were done with SiCl<sub>4</sub> gas, ICP power of 100 W and 50 W, respectively, bias power of 20 W, SiCl<sub>4</sub> gas flow rate of 3 sccm and working chamber pressure of 0.25 Pa (termed as: No. 1 SiCl<sub>4</sub> 100W/20W and No. 2 SiCl<sub>4</sub> 50W/20W, respectively). The etching rates of these two samples were about 1.2 nm/min and 1.0 nm/min, respectively. Sample No. 3 was etched with mixed BCl<sub>3</sub>/Cl<sub>2</sub> gas (20/20 sccm), ICP power of 100 W, bias power of 25 W and at a working chamber pressure of 0.6 Pa. The etching depths were 110 nm and 60 nm respectively (termed as: No. 3 BCl<sub>3</sub>/Cl<sub>2</sub>, 60 nm), and the etching rates were about 30 nm/min.

During the etching processes, the sample stage was cooled by helium gas to keep at the room temperature.

|     | rucio 2. o recouss comments or un uno sumpress |       |       |                                   |        |          |          |        |

|-----|------------------------------------------------|-------|-------|-----------------------------------|--------|----------|----------|--------|

|     |                                                | ICP   | Bias  |                                   | Flow   | Chamber  | Etching  | Recess |

| No. | Term                                           | Power | Power | Gas                               | Rate   | Pressure | Rate     | Depth  |

|     |                                                | (W)   | (W)   |                                   | (sccm) | (Pa)     | (nm/min) | (nm)   |

| 1   | SiCl <sub>4</sub> 100W/20W                     | 100   | 20    | SiCl <sub>4</sub>                 | 3      | 0.25     | 1.2      | 60     |