#### **Abstract**

AlGaN/GaN HFETs have become the subject of competing research due to the superior material properties of GaN. An urgent need is to reduce the leakage current in the field of high temperature and high frequency. In our previous works, AlGaN/GaN HFETs with the Schottky gates have the relatively higher reverse leakage current. For AlGaN/GaN HFETs, there is an urgent need to find p-type semiconductor gate materials and insulator gate materials with high k and high crystallization temperatures for their normally-off and high temperature applications. In this thesis, we discussed the synthesis and application of oxide for GaN electron devices.

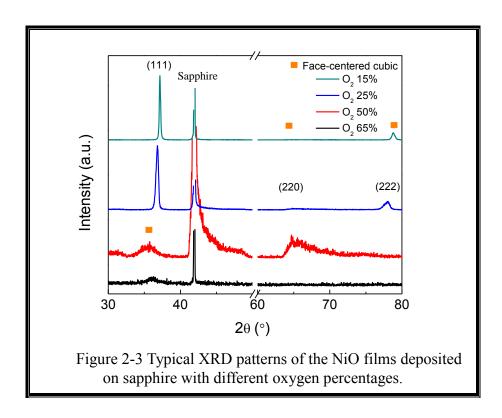

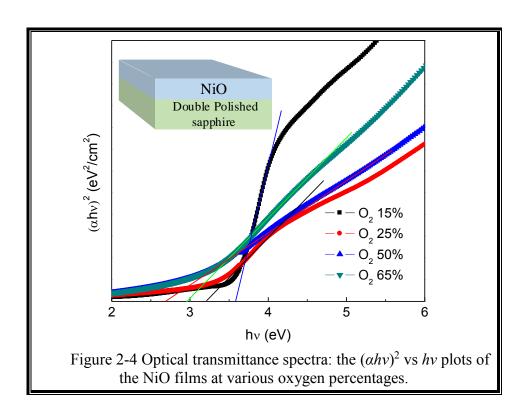

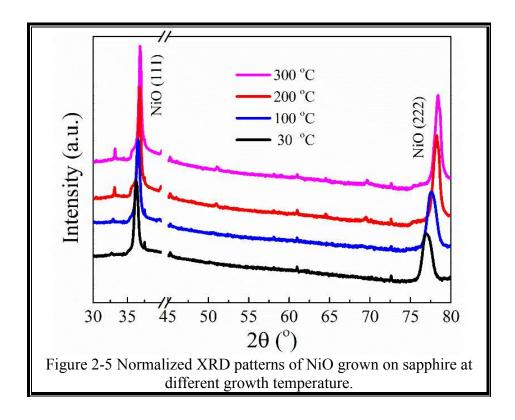

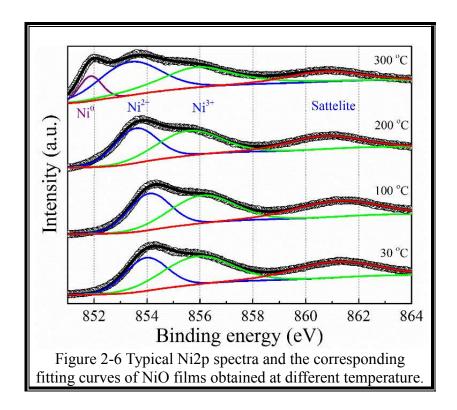

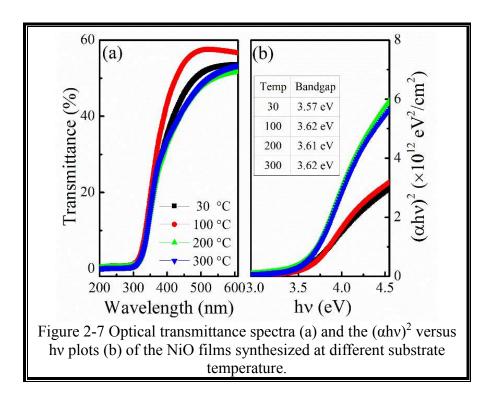

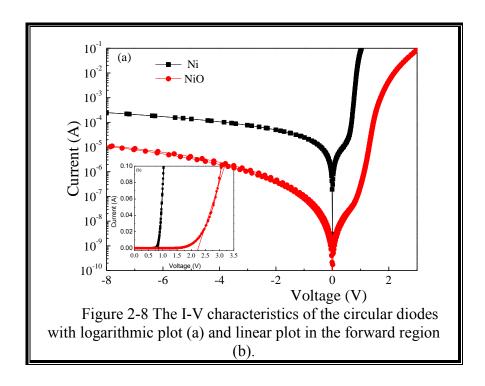

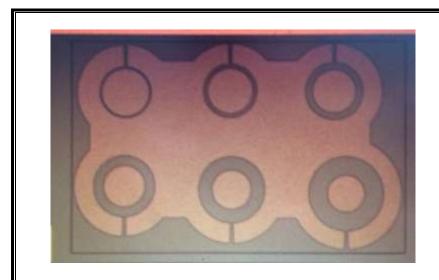

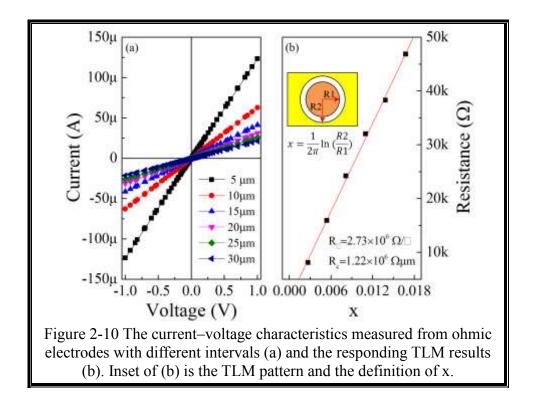

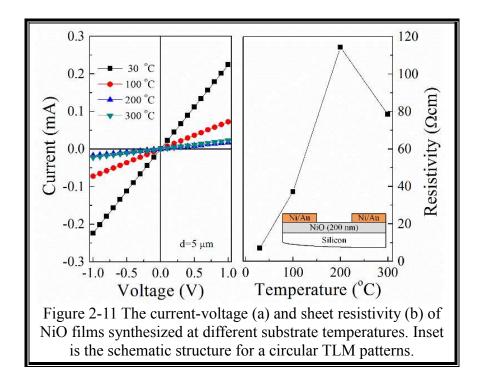

NiO is a natural p-type semiconductor with stable chemical properties. We fabricated NiO films with different O<sub>2</sub>/Ar ratios of 15%, 25%, 50%, and 65% and substrate temperature from 30 to 300 °C using magnetron reactive sputtering. The NiO films with the face-centered cubic crystalline structure are analyzed by AFM, XRD, XPS, UV-Vis transmittance spectra and circular TLM. The crystal orientation depends on the oxygen percentage. The quality of the crystallization decreases with the increasing of oxygen percentage. When the substrate temperature increased from 30 to 200 °C, the crystalline quality and stoichiometric of the NiO films were improved, resulting in higher bandgap value and resistivity. While further increasing the substrate temperature to 300 °C, the decomposition of NiO will cause the appearance of Ni metal in the film. An optimal oxygen ratio of 25% under substrate temperature of 30 °C for growing NiO is obtained.

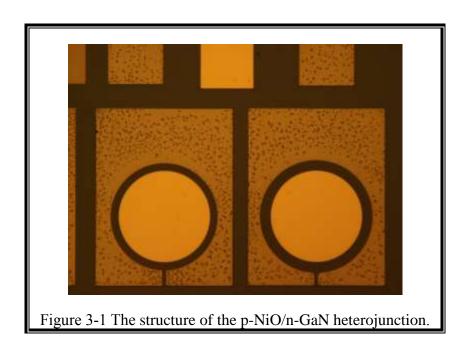

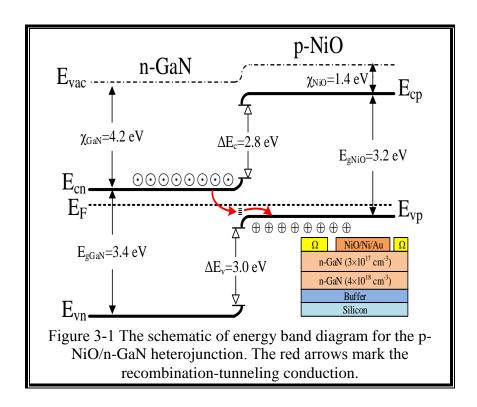

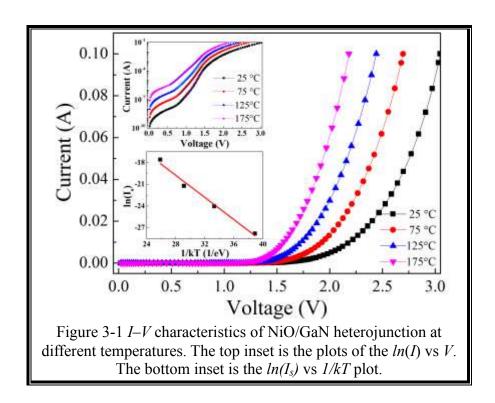

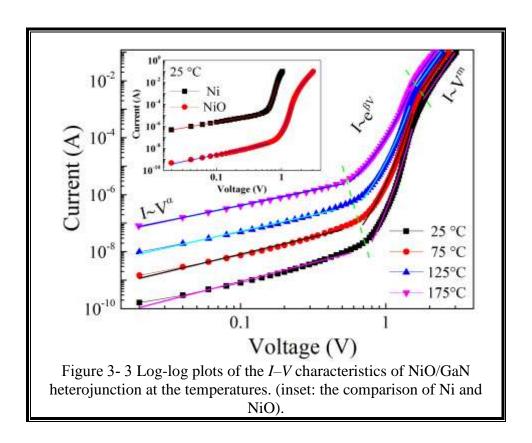

The electrical transport properties of the NiO/GaN heterojunction device in the temperature range from 25 to 175 °C is investigated. Comparing with the Ni/GaN Schottky diode, the turn-on voltage of the NiO/GaN heterojunction diode is relatively higher. The NiO/GaN diode exhibited a temperature-dependent turn-on voltage with smaller reverse leakage current. The as-grown NiO exhibited cubic crystalline structure with a bandgap of 3.2 eV. It is founded that there are three types of current transport mechanisms which are strongly relates to the applied bias voltages and temperatures. On the other hand, the device exhibited considerably a stable behavior over the temperature range from 25 to 175 °C and will be favorable for widely applying in high-temperature and high-power environments.

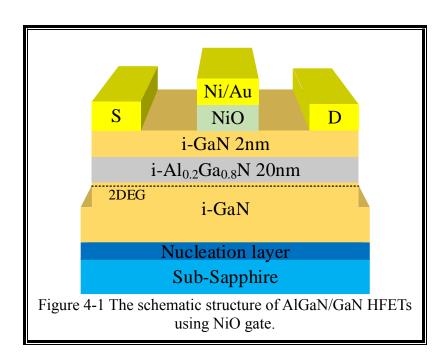

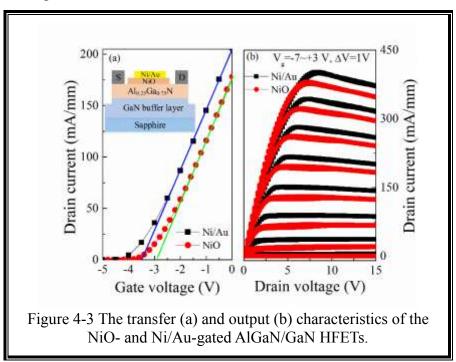

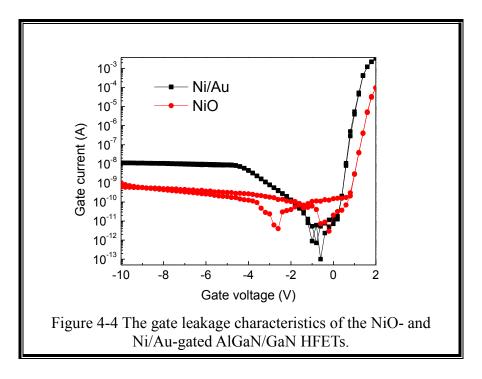

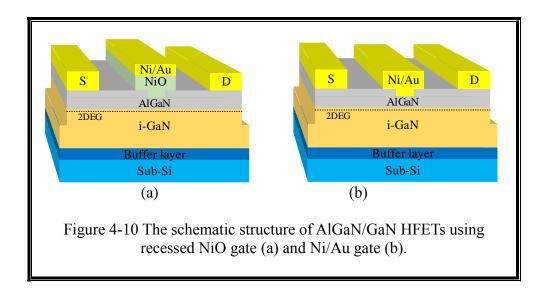

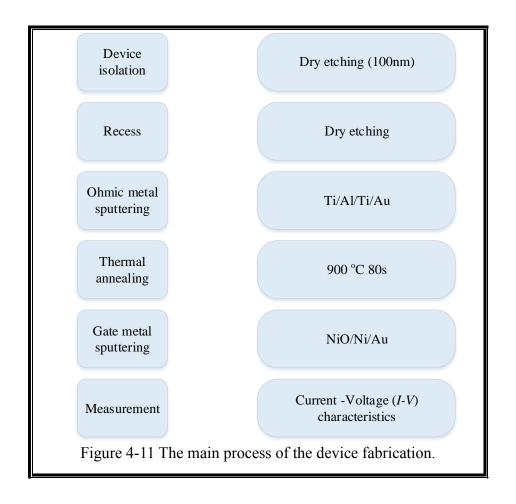

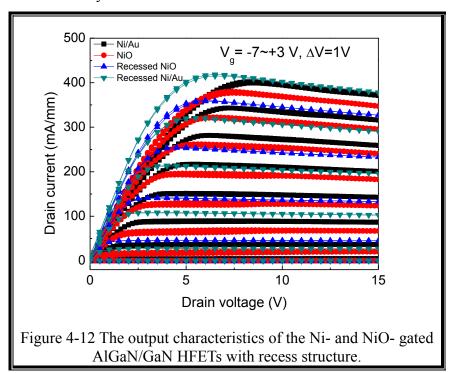

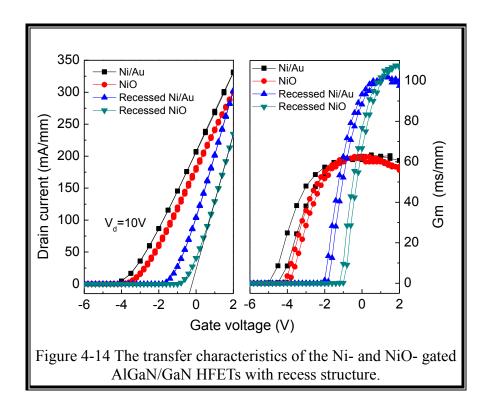

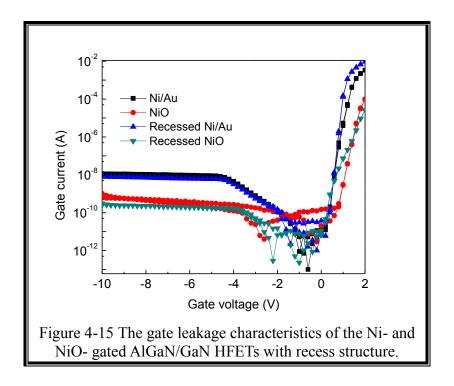

From above the material and electrical results, we used the NiO film under 30 °C with

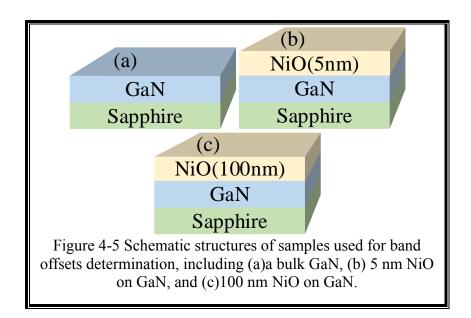

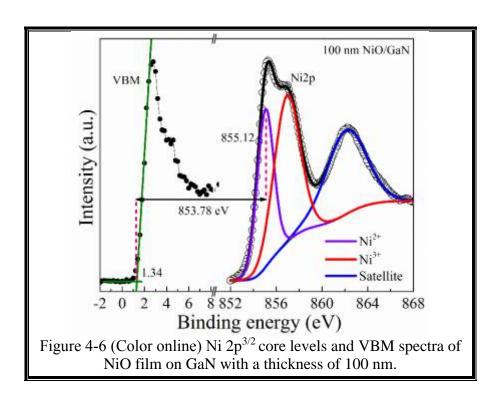

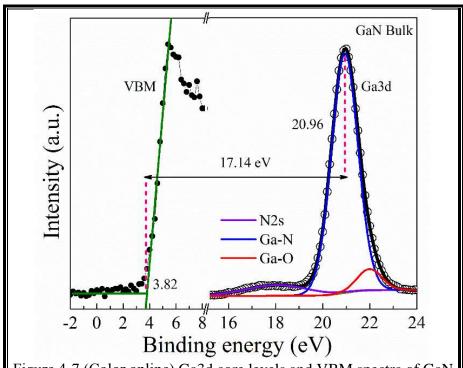

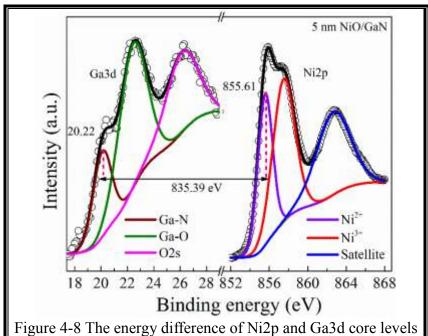

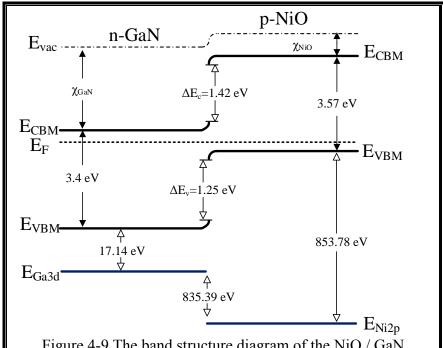

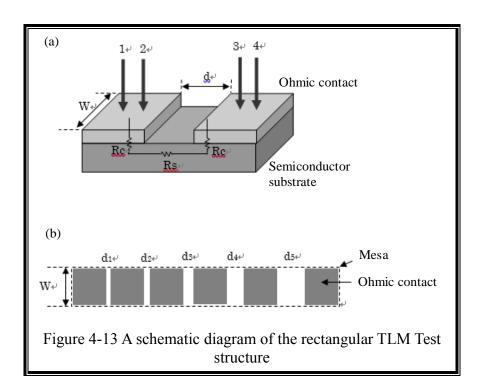

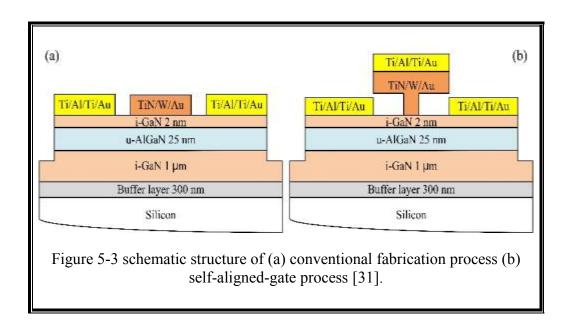

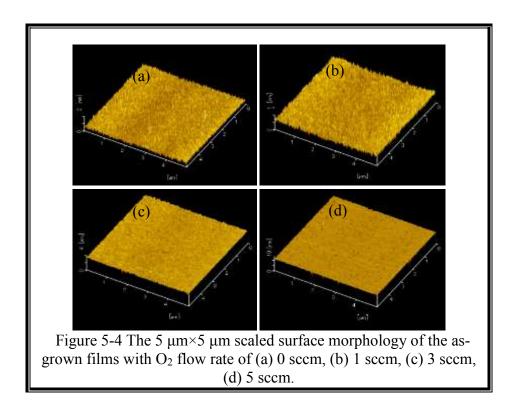

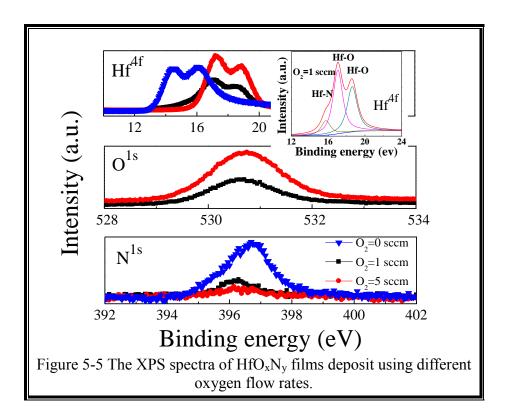

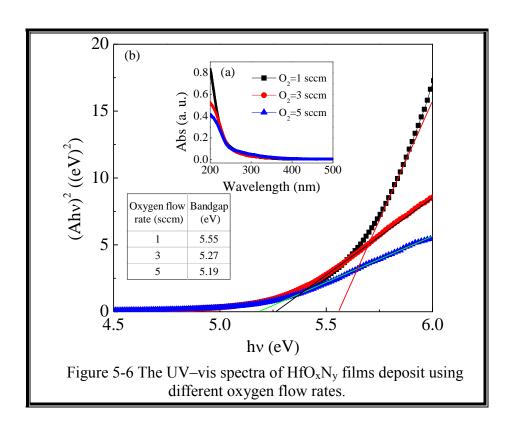

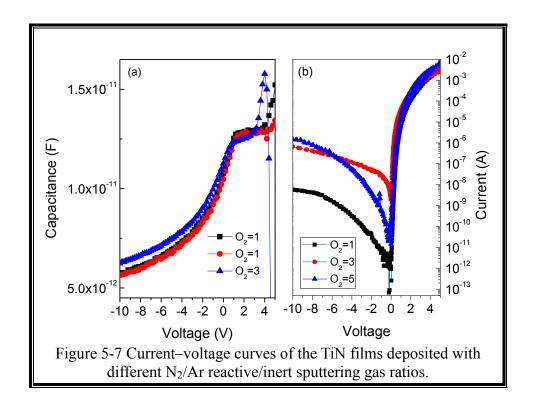

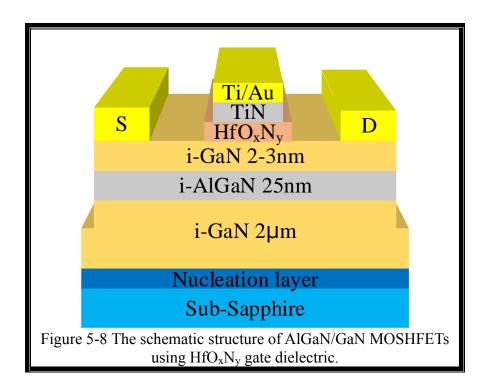

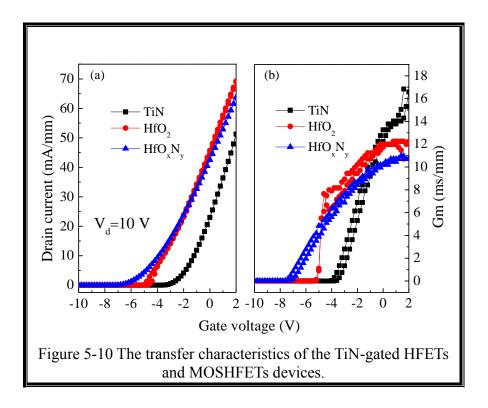

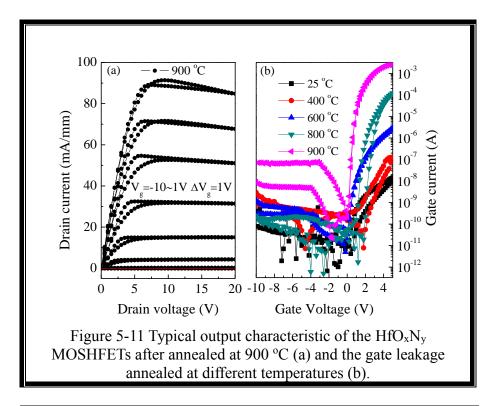

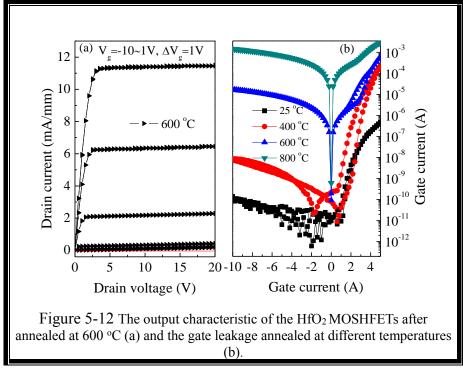

lowest resistivity as the gate electrode for AlGaN/GaN HFETs application. Compared with the Ni/Au-gated device, the threshold voltage of the NiO-gated device has a positive shift of approximately 1V because of the p-type conductivity as well as the conduction band offsets between NiO and GaN. The band offset at the heterojunction interface can be measured by XPS employing a well-known Kraut's method. We calculated the corresponding valence (1.25 eV) and conduction band offset (1.42 eV) using a band gap of 3.57 eV for the NiO film deposited at 30 °C. After recessing, the threshold voltage for the Ni- and NiO-gated HFETs has a positive shift. We obtained normally-off NiO-gated GaN HFETs with a threshold voltage of closing to 0 V using the recessed-gate structure. As one of the most promising insulator candidates, HfO<sub>2</sub> and HfO<sub>x</sub>N<sub>y</sub> with wide bandgap and high-k are extensive investigated. We fabricated HfO<sub>x</sub>N<sub>y</sub> films with different oxygen flow rates using magnetron reactive sputtering. The films are analyzed by AFM, XPS, UV-Vis diffuse reflection spectra. The growth rate decreases with the increasing of oxygen flow rate. The quantity of the hole increases with increasing oxygen flow rate. The composition of films changed from HfN to HfO<sub>2</sub> domination with the increasing oxygen flow rate and HfO<sub>x</sub>N<sub>y</sub> formed at a smaller oxygen flow rate. MOS diode fabricated with HfO<sub>x</sub>N<sub>y</sub> film by 1 sccm oxygen shows the smallest reverse leakage current. It indicates that the HfO<sub>x</sub>N<sub>y</sub> film is made due to the higher nitrogen in the reactive gases. We fabricated AlGaN/GaN HFETs using TiN/HfO<sub>x</sub>N<sub>y</sub> stack gate layer with 1 sccm oxygen. The threshold voltage for the Schottky contact, HfO<sub>2</sub> MOS, and HfO<sub>x</sub>N<sub>y</sub> MOS HFETs are approximately -3.0, -5.0, and -7.0 V, respectively. Compared with HfO<sub>2</sub> MOSHFETs, the introduction of the HfO<sub>x</sub>N<sub>y</sub> dielectric results in a negative shifting threshold voltage and a lower leakage current. After post deposition annealing at different temperatures, the devices using HfO<sub>x</sub>N<sub>y</sub> dielectric show better thermal stability at 900 °C while obvious degradation are observed for the HfO<sub>2</sub> MOSHFETs at 600 °C. A possible mechanism is that the existence of Hf-N bond in bulk dielectric and N at the dielectric/GaN interface can help to improve the thermal stability. The thermal stability of TiN/HfO<sub>x</sub>N<sub>y</sub>/AlGaN/GaN HFETs shows that the HfO<sub>x</sub>N<sub>y</sub> dielectric is a promising candidate for the self-aligned gate process.

**Keywords:** AlGaN/GaN, HFETs, NiO, HfO<sub>x</sub>N<sub>v</sub>

# Outline

| Chapter 1: Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1 -                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| §1.1. Background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1 -                                                                                |

| §1.2. The AlGaN/GaN HFETs Technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3 -                                                                                |

| §1.3. The motivation of this reaserch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                    |

| §1.4. Outline of thesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                    |

| §1.5. Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                    |

| Chapter 2: Synthesis and characterization of NiO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 17 -                                                                               |

| §2.1. Selection of material                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 17 -                                                                               |

| §2.2. The synthesis of NiO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                    |

| §2.2.1. The synthesis of NiO films with different oxygen ratio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                    |

| §2.2.2. The synthesis of NiO films at different substrate temperatures                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                    |

| §2.3. The characteristics of NiO films                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                    |

| §2.3.1. The properties of NiO films with different oxygen ratio                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                    |

| §2.3.2. The properties of NiO films with different substrate temperatures<br>§2.4. The contact of materials on n-GaN                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                    |

| §2.5. The resistivity of NiO film                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                    |

| §2.5.1. The resistivity of NiO film with different oxygen ratio                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                    |

| §2.5.2. The resistivity of NiO film with different substrate temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                    |

| §2.6. Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                    |

| §2.7. Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 35 -                                                                               |

| Chapter 3: Temperature–dependent electrical transport characteristics of a NiO/GaN heterojunction diode                                                                                                                                                                                                                                                                                                                                                                                                                                       | 39 -                                                                               |

| §3.1. GaN-based heterojunction diode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | - 39 -                                                                             |

| §3.2. Fabrication of the NiO/GaN heterojunction diode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                    |

| §3.3. The characterization of a NiO/GaN heterojunction diode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                    |

| §3.4. Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                    |

| 02 5 D C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 47 -                                                                               |

| §3.5. Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                    |

| \$3.5. Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                    |

| Chapter 4: Normally-off AlGaN/GaN HFETs with NiO gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 49 -                                                                               |

| v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <b>49</b> -                                                                        |

| Chapter 4: Normally-off AlGaN/GaN HFETs with NiO gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>49</b> -<br>49 -<br>50 -                                                        |

| Chapter 4: Normally-off AlGaN/GaN HFETs with NiO gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 49 -<br>49 -<br>50 -<br>50 -                                                       |

| State Chapter 4: Normally-off AlGaN/GaN HFETs with NiO gate  §4.1. Normally-off (or E-mode) AlGaN/GaN HFETs  §4.2. The fabrication of NiO-gated AlGaN/GaN HFETs  §4.3. The characteristics of NiO-gated AlGaN/GaN HFETs  §4.4. The fabrication of NiO-gated normally-off AlGaN/GaN HFETs  §4.5. The characteristics of NiO-gated normally-off AlGaN/GaN HFETs                                                                                                                                                                                 | 49 -<br>49 -<br>50 -<br>50 -<br>57 -<br>59 -                                       |

| Chapter 4: Normally-off AlGaN/GaN HFETs with NiO gate  §4.1. Normally-off (or E-mode) AlGaN/GaN HFETs  §4.2. The fabrication of NiO-gated AlGaN/GaN HFETs  §4.3. The characteristics of NiO-gated AlGaN/GaN HFETs  §4.4. The fabrication of NiO-gated normally-off AlGaN/GaN HFETs  §4.5. The characteristics of NiO-gated normally-off AlGaN/GaN HFETs  §4.6. Conclusion                                                                                                                                                                     | 49 -<br>49 -<br>50 -<br>50 -<br>57 -<br>59 -<br>62 -                               |

| State Chapter 4: Normally-off AlGaN/GaN HFETs with NiO gate  §4.1. Normally-off (or E-mode) AlGaN/GaN HFETs  §4.2. The fabrication of NiO-gated AlGaN/GaN HFETs  §4.3. The characteristics of NiO-gated AlGaN/GaN HFETs  §4.4. The fabrication of NiO-gated normally-off AlGaN/GaN HFETs  §4.5. The characteristics of NiO-gated normally-off AlGaN/GaN HFETs                                                                                                                                                                                 | 49 -<br>49 -<br>50 -<br>50 -<br>57 -<br>59 -<br>62 -                               |

| Chapter 4: Normally-off AlGaN/GaN HFETs with NiO gate  §4.1. Normally-off (or E-mode) AlGaN/GaN HFETs  §4.2. The fabrication of NiO-gated AlGaN/GaN HFETs  §4.3. The characteristics of NiO-gated AlGaN/GaN HFETs  §4.4. The fabrication of NiO-gated normally-off AlGaN/GaN HFETs  §4.5. The characteristics of NiO-gated normally-off AlGaN/GaN HFETs  §4.6. Conclusion  §4.7. Reference  Chapter 5: Metal-oxide-semiconductor AlGaN/GaN HFETs using TiN/HfOxI                                                                              | 49 -<br>49 -<br>50 -<br>57 -<br>59 -<br>62 -<br>65 -                               |

| Chapter 4: Normally-off AlGaN/GaN HFETs with NiO gate  §4.1. Normally-off (or E-mode) AlGaN/GaN HFETs  §4.2. The fabrication of NiO-gated AlGaN/GaN HFETs  §4.3. The characteristics of NiO-gated AlGaN/GaN HFETs  §4.4. The fabrication of NiO-gated normally-off AlGaN/GaN HFETs  §4.5. The characteristics of NiO-gated normally-off AlGaN/GaN HFETs  §4.6. Conclusion  §4.7. Reference  Chapter 5: Metal-oxide-semiconductor AlGaN/GaN HFETs using TiN/HfOxI stack gate layer                                                             | 49 -<br>49 -<br>50 -<br>50 -<br>57 -<br>59 -<br>62 -<br>65 -<br>Ny<br>67 -         |

| Chapter 4: Normally-off AlGaN/GaN HFETs with NiO gate  §4.1. Normally-off (or E-mode) AlGaN/GaN HFETs  §4.2. The fabrication of NiO-gated AlGaN/GaN HFETs  §4.3. The characteristics of NiO-gated AlGaN/GaN HFETs  §4.4. The fabrication of NiO-gated normally-off AlGaN/GaN HFETs  §4.5. The characteristics of NiO-gated normally-off AlGaN/GaN HFETs  §4.6. Conclusion  §4.7. Reference  Chapter 5: Metal-oxide-semiconductor AlGaN/GaN HFETs using TiN/HfOxI stack gate layer  §5.1. Selection of material                                | 49 -<br>49 -<br>50 -<br>57 -<br>59 -<br>62 -<br>65 -<br>Ny<br>67 -                 |

| Chapter 4: Normally-off AlGaN/GaN HFETs with NiO gate  §4.1. Normally-off (or E-mode) AlGaN/GaN HFETs  §4.2. The fabrication of NiO-gated AlGaN/GaN HFETs  §4.3. The characteristics of NiO-gated AlGaN/GaN HFETs  §4.4. The fabrication of NiO-gated normally-off AlGaN/GaN HFETs  §4.5. The characteristics of NiO-gated normally-off AlGaN/GaN HFETs  §4.6. Conclusion  §4.7. Reference  Chapter 5: Metal-oxide-semiconductor AlGaN/GaN HFETs using TiN/HfOxI stack gate layer  §5.1. Selection of material  §5.2. The synthesis of HfOxNy | 49 -<br>49 -<br>50 -<br>50 -<br>57 -<br>62 -<br>65 -<br>Ny<br>67 -<br>72 -         |

| Chapter 4: Normally-off AlGaN/GaN HFETs with NiO gate  §4.1. Normally-off (or E-mode) AlGaN/GaN HFETs  §4.2. The fabrication of NiO-gated AlGaN/GaN HFETs  §4.3. The characteristics of NiO-gated AlGaN/GaN HFETs  §4.4. The fabrication of NiO-gated normally-off AlGaN/GaN HFETs  §4.5. The characteristics of NiO-gated normally-off AlGaN/GaN HFETs  §4.6. Conclusion  §4.7. Reference  Chapter 5: Metal-oxide-semiconductor AlGaN/GaN HFETs using TiN/HfOxI stack gate layer  §5.1. Selection of material                                | 49 -<br>49 -<br>50 -<br>50 -<br>57 -<br>62 -<br>65 -<br>Ny<br>67 -<br>72 -<br>72 - |

| §5.2.3. Characteristics of MOS diode using HfO <sub>x</sub> N <sub>y</sub>                     | 76 -     |

|------------------------------------------------------------------------------------------------|----------|

| §5.3. Thermal stability studies of Metal-oxide-semiconductor AlGaN/GaN H                       | FETs     |

| using TiN/HfO <sub>x</sub> N <sub>y</sub> stack gate layer                                     | 77 -     |

| §5.3.1. The fabrication of TiN/HfO <sub>x</sub> N <sub>y</sub> /AlGaN/GaN HFETs                | 77 -     |

| §5.3.2. The characteristics of TiN-gated and MOSHFETs devices                                  | 79 -     |

| §5.3.3 The characteristics of TiN/HfO <sub>x</sub> N <sub>y</sub> /AlGaN/GaN HFETs with anneal | ing 81 - |

| §5.4. Conclusion                                                                               | 82 -     |

| §5.5. Reference                                                                                | 85 -     |

| Chapter 6: Conclusions and future works                                                        | 89 -     |

| §6.1. Summary and conclusions                                                                  | 89 -     |

| §6.2. Suggestion for future works                                                              |          |

| Acknowledgements                                                                               | 92 -     |

| Biography                                                                                      | 93 -     |

| Publication list                                                                               | 94 -     |

# **Chapter 1: Introduction**

### §1.1. Background

With the development of technology and society, the efficient and practical use of electric energy is a hot issue that has caught people's attention. Power electronics technology is a discipline of the realization for power conversion and control. It is a bridge and link of weak electricity controlling strong electricity. It is now widely used in various fields such as industrial and agricultural production, national defense, transportation, energy and people's livelihood. Of course, the emergence and development of power electronics depend on the continuous development of power electronics devices. In 1948, the invention of the first generation of semiconductor transistors gradually led to an electronic industrial revolution. The first semiconductor transistor was used in the field of low-power, such as computers. With the advent of the world's first transistor, the range of semiconductor transistors have been greatly expanded. Power conversion and control was developed from the rotating converter unit, the static ion converter into the inverter composed of the power semiconductor devices, which also marks the birth of power electronics technology. Transistors have played an important role in the establishment of power electronics disciplines. But the transistor is a semi-controlled device, which cannot control its pinch-off. So far, due to their relatively low cost, transistors and their derivatives have been widely used in various converters.

Due to the first generation semiconductor devices can only control its conduction through its gate and can not control its pinch-off, it was necessary to add inductors, capacitors or other auxiliary switching devices to turn off it in the DC power. But these will let increase the size of the current transformer and reduce the efficiency. The power electronic devices of the second generation represented by Giant Transistor (GTR) [1], Gate Turn-Off Thyristor (GTO) [2,3], MOSFET [4]. They can be controlled to turn on and off. The power electronics MOSFET of the second generation is a unipolar device, which is no conductivity modulation effect and increases its switching speed. And MOSFET became the most important power semiconductor devices in the high-frequency field. However, it is precisely because of no conductivity modulation effect, as the device

withstand voltage increases, on-resistance of MOSFET also increases, which will lead to have very serious conduction losses.

By the late 1980s, composite devices represented by insulated gate bipolar transistors (IGBTs) appeared [5]. IGBT is a combination of MOSFET and GTR, which is a MOSFET-driven bipolar transistor. It has advantage of both the MOSFET's high input impedance and GTR's low on-voltage drop. However, with the development of science and technology, IGBTs still can not meet the demanding requirements in various fields such as aerospace, communications and nuclear energy. People urgently need a power electronic device that can still work normally under the extreme conditions of high temperature and high radiation. Therefore, we must find more advantageous materials to develop high-power electronic devices for meeting the high temperature, high frequency, high radiation environment. Therefore, new materials such as GaAs, GaAlAs, SiC, diamond and GaN have been rapidly developed and applied [6-10].

Because of their excellent properties and thermal stability, the group III nitrides are determined to play a pivotal role in the future development of optoelectronic devices [11, 12]. Among the many group III nitrides, the gallium nitride (GaN) is seen as the preferred material of the blue and other short-wavelength optical devices (especially blue laser diodes and blue light-emitting diodes) [13-16]. And that it can meet the requirements of the semiconductor devices with high power, high temperature, high frequency and high speed, which are not available with many silicon (Si)-based semiconductor materials. Although the related properties of GaN films have been studied in the last few decades, the GaN films produced often have relatively high defect density due to the backwardness of the thin film preparation technology at that time. So that, the relevant research of the GaN material was not satisfactory. Recently, with the increase of the GaN film growth technology, high quality GaN thin film can be grown by Molecular Beam Epitaxy (MBE), Metal-organic Chemical Vapor Deposition (MOCVD) and Solid Phase Epitaxy (SPE). In some related reports, most of the GaN films were grown on the wide variety of substrates such as Si [17-22], gallium arsenide (GaAs) [23-26] and silicon carbide (SiC) [27,28]. However, it is difficult to grow high quality GaN films on these substrates because of the large lattice mismatch and the imbalance of the coefficient with thermal expansion between these substrates and the GaN films. In order to further improving the quality of GaN films, the buffer layers between GaN films and commonly used monocrystalline

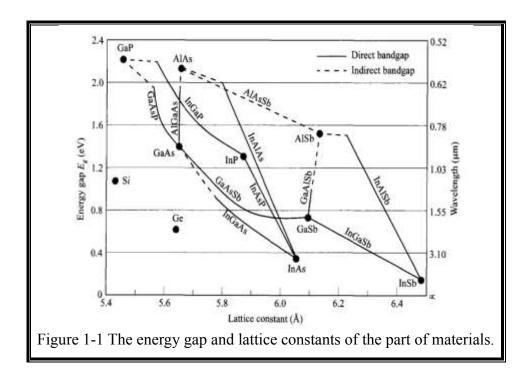

substrates were grown to overcome the adverse effects of the lattice mismatch and thermal expansion coefficients between GaN layer and substrates. The buffer layers used in the experiments generally include aluminum nitride (AlN), SiC, GaAs, oxidized aluminum arsenide (AlAs) [29-32], and so on. High quality GaN films were successfully grown on the (0001) sapphire (Al<sub>2</sub>O<sub>3</sub>) substrates by low-pressure metal organic chemical vapor deposition (LP-MOCVD). The LP-MOCVD technology is critical to improving the quality of the GaN films due to the remission of the adverse effect with lattice mismatch (13%~16%) between GaN films and sapphire substrates [33]. Figure 1-1 shows the energy gap and lattice constants of the part of materials.

## §1.2. The AlGaN/GaN HFETs Technology

AlGaN/GaN heterostructure field-effect transistor (HFET) also called high electron mobility transistor (HEMT), is an important representative of GaN electronic devices. It is the focus of development and competition in the third generation semiconductor technology field. Because of its application prospects in the high temperature, high frequency, high power fields, AlGaN/GaN heterostructure becomes one of the hot spots in recent years. From the perspective of output power and frequency, AlGaN/GaN HFETs

are very suitable for high-frequency and high-power applications such as wireless communication base stations, radar and automotive electronics. In the aerospace, nuclear industry, military electronics, which require high chemical and thermal stability, AlGaN/GaN HFET is also one of the ideal candidate devices. These mainly benefits are from wide-bandgap, chemical stability and superior electrical characteristics of GaN.

Unlike SiC electronic devices, which depend on the electron mobility of the bulk materials, GaN-based materials are easy to fabricate heterostructure and can take full advantage of the superior properties of 2DEG. The AlGaN/GaN heterojunction material is one of the important representatives. It was reported that the carrier mobility can reach 2019 cm<sup>2</sup>/V·S at 300K for the Al<sub>0.22</sub>Ga<sub>0.78</sub>N heterojunction [34]. Besides, the highest mobility reached 5.17 × 10<sup>4</sup> cm<sup>2</sup>/V·S for the Al<sub>0.09</sub>Ga<sub>0.91</sub>N heterostructure at 13K [35]. Hence, AlGaN/GaN heterostructure has a more advantage than SiC in the manufacture of high frequency microwave devices. Table 1-1 shows the properties of several semiconductor materials.

GaN-based transistors, especially AlGaN/GaN HFETs have become a candidate of solid-state microwave power devices because of their performance to generate higher power densities at higher frequencies. The GaN-based material has unique properties of wide bandgap (3.4 eV of GaN to 6.2 eV of AlN), large breakdown electric field strength ( $\sim 3.3 \times 10^6$  V / cm) and high saturation electron drift velocity ( $>2 \times 10^7$  cm/s).

Chapter 1: Introduction

|                                         | Si                | 6H-SiC        | GaN                              | GaAs              |

|-----------------------------------------|-------------------|---------------|----------------------------------|-------------------|

| Bandgap (eV)                            | 1.12              | 3.21          | 3.4                              | 1.42              |

| Lattice consta<br>nt (nm)               | 0.543             | 0.308         | 0.319                            | 0.565             |

| Dielectric constant                     | 11.9              | 10.32         | 10.4                             | 12.9              |

| Thermal conductivity (W/cmK)            | 1.56              | 4.9           | 1.3                              | 0.46              |

| Electron mobility (cm <sup>2</sup> /Vs) | 1450              | 400           | 1200<br>(bulk)<br>2000<br>(2DEG) | 8000              |

| Breakdown field (V/cm)                  | 3×10 <sup>5</sup> | $3\times10^6$ | $3.3 \times 10^6$                | 4×10 <sup>5</sup> |

Table 1-2 Properties of main semiconductors.

Furthermore, the AlGaN/GaN heterostructure materials can generate 2DEG of ~10<sup>13</sup> /cm² in the quantum well of the AlGaN/GaN heterostructure interface by polarized stress without any dopant, which much higher than the other III-V heterostructure materials system. The main reason is the strong spontaneous polarization and piezoelectric polarization effect exists in the AlGaN/GaN heterostructure materials. The higher density of 2DEG makes AlGaN/GaN HFETs have higher output current density. Coupling with the higher capability of withstand voltage, the transistors have typically higher output power density and are suitable for use in high power applications.

In summary, AlGaN/GaN HFETs have mainly four advantages.

Firstly, AlGaN/GaN HFETs have higher 2DEG density. Due to the strong polarization effect of AlGaN/GaN heterostructure, the density of 2DEG for the undoped AlGaN/GaN heterostructure can be as high as ~10<sup>13</sup> /cm<sup>2</sup>, which has one order of magnitude higher than that of the AlGaAs/GaAs heterostructure [36]. In addition, AlGaN/GaN HFETs have the superior characteristics, such as high transconductance, high saturation current and high cut-off frequency, owe to 2DEG electron mobility greatly enhancing.

Secondly, AlGaN/GaN HFETs can work at high temperature. The band gap of GaN is 3.4eV, which is three times that of Si and twice that of GaAs. AlGaN/GaN HFETs are suitable for high temperature work due to accurately controlling the free carrier

concentration in a considerable temperature range. Consequently, GaN-based devices have a higher work temperature than Si and GaAs based devices. In addition, GaN has high thermal conductivity that is three times that of GaAs, which effectively improves the heat dissipation characteristics of the devices and makes the GaN-based devices have better reliability under a high temperature environment.

Thirdly, AlGaN/GaN HFETs have well power characteristics. Because the breakdown electric field of GaN material is up to 3.3 MV/cm, AlGaN/GaN HFETs can work under high bias. In addition, the output power density of AlGaN/GaN HFETs on the SiC substrate is up to 10 W/mm, which is 20 times higher than GaAs-based devices. This reduces the size of the power device, improves the reliability of the device and reduces the fabricating cost of the device.

Finally, AlGaN/GaN HFETs have the strong anti-radiation ability. Due to the high chemical bond energy of the GaN material, the physical and chemical properties of the material is stable. It is not susceptible to external physical and chemical effects. Therefore, the devices of the GaN-based HFETs have better anti-radiation ability than GaAs-based devices. Combined with its high power density, AlGaN/GaN HFETs will be the best solid-state power devices for satellites with the comprehensive advantages of high power, small size, light weight and strong anti-radiation ability.

Therefore, AlGaN/GaN HFETs have broad application prospect in the fields of high temperature, high frequency and high power due to its superior electrical characteristics. And it has become a research hotspot in the field of microelectronic devices in recent years. Therefore, in-depth study of the basic characteristics of AlGaN/GaN HFETs is great significance for its development and real application.

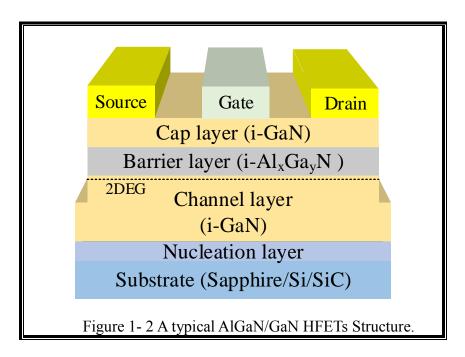

Figure 1-2 shows a typical AlGaN/GaN HFETs structure. MOCVD and MBE methods are usually used to grow the GaN-based HFETs epitaxial layers structure. The structure of AlGaN/GaN HFETs mainly consists five parts (from bottom to top): substrate, nucleation layer, channel layer, barrier layer, and cap layer.

Sapphire, Si and SiC are usually used as the substrate for AlGaN/GaN HFETs. Their properties are shown in Table 1-1. The lattice mismatch exists between these substrates and GaN. Where the lattice mismatch between SiC and GaN is minimal, but the manufacturing cost is relatively high.

To reduce stress and lattice mismatch from the nonnative substrate, nucleation layer is first grown on the substrates. And very thin AlN, AlGaN or GaN layer are usually used as the nucleation layer.

Channel layer (GaN in our case) is a material with the semi-insulating (SI) or high resistivity which is to ensure complete channel pinch-off, low loss at high frequencies, low cross-talk between adjacent devices and proper drain-source current saturation. On the side, the channel layer has a lower bandgap than barrier layer.

After growing the thicker channel layer, a 20 nm thickness Al<sub>x</sub>Ga<sub>y</sub>N layer is grown as the barrier layer, which is the most critical layer in HEMT structure. The bandgap of this material depends on the aluminium mole fraction x and is higher than the channel layer [37].

Chapter 1: Introduction

Cap layer is deposited on top of the barrier layer, which is beneficial to prevent the form low resistance Ohmic contact, act as gate insulate, oxidation of barrier layer surface, etc. [38, 39] It is usually a 1-2 nm thick GaN layer.

By optical lithography and reactive sputtering technology, three metal electrodes, source (S), gate (G), and drain (D), are formed on the top cap layer. Both the source and drain terminals are ohmic contacts.

The source is typically grounded. The drain with a positive bias can control the flow of carriers in the 2DEG from the source to the drain in a direction parallel to the heterogeneous interface. The potential distribution of the heterostructure can be controlled by the gate. The structure of gate has generally the following three kinds: Schottky contact, p-n junction and metal-insulator-semiconductor (MIS).

In our previous work, Ni and TiN electrodes are normally used to develop GaN Schottky diode. TiN has lower turn-on voltage and comparable breakdown voltage comparing with Ni. However, the reverse leakage current is relative higher [40]. To suppress the reverse leakage current, new gate structure is necessary.

# §1.3. The motivation of this reaserch

In the realization of GaN power switching device industrialization, there are still facing with many technical difficulties. Based on the viewpoint of safety, normally-off operation is strongly required. At present, there are three ways to fabricate the normally-off type GaN devices: junction gate structure (p-type gate), cascode structure and trench gated MOSFET. At present, the first two structures have been achieved industrialization. However, multi-chip packaging for Cascode normally-off GaN devices reduces the reliability of the device, and the p-type gated normally-off GaN devices has the small threshold voltage, the large gate leakage, the small gate voltage swing redundancy and the bad resistance to electromagnetic interference. The structure of the trench gate is expected to replace the above-mentioned methods because of its large gate voltage swing redundancy and small gate leakage current.

Because the 2DEG density has to be reduced to obtain the normally-off characteristics, we can choose the p-type oxide layer as recessed gate material.

In addition, the AlGaN/GaN HFETs are considered as the most promising materials for

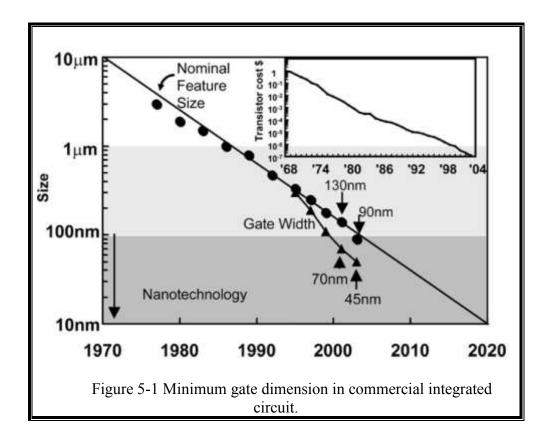

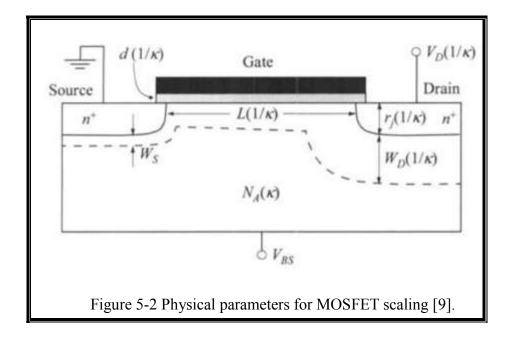

high-frequency and high-power electronic devices. It is satisfactory to provide a gate contact with large Schottky barrier height (SBH) and prominent thermal stability to achieve the high-temperature performance. To achieve a high-temperature performance, it is very desirable to produce a gate contact with a large SBH and an excellent thermal stability. In the applications of high-frequency, a self-aligned gate (SAG) process comes up with minimizing the distances of source-to-gate and drain-to-gate for a smaller access resistance, in which a T-shaped Schottky gate is firstly manufactured and then applied to a mask directly for ohmic metal formation.

After that, the Schottky gate and the ohmic electrodes are treated by annealing synchronously to attain ohmic contacts. Establishing the Schottky gate is a significant method which can stand up to ohmic annealing process in order to constitute the SAG structure, due to the optimal annealing temperature for ohmic contact of the Ti-based multilayers on GaN-based materials is approximately 800 to 850 °C. Therefore, the Schottky gate must be capable of withstanding such a high temperature during the annealing process of source-drain ohmic contact. In previous studies, Ao-lab has evaluated the electrical performance of Schottky contacts fabricated by many different types of refractory metal nitrides, such as HfN, TiN, MoSiN, MoN, TaN, ZrN and WTiN on GaN deposited by reactive sputtering in Ar and N<sub>2</sub> mixed ambient environment. Take many factors into consideration, such as adhesion on GaN, sheet resistivity, reverse leakage current, SBH, and thermal stability of these devices, TiN is considered as one of the most suitable materials for the Schottky electrodes. It is easy to obtain by a simple method reactive sputtering with nitrogen ambient environment and shows a relatively smaller resistivity, better adhesion, and smaller leakage current of the GaN Schottky contact. To suppress the leakage current of the AlGaN/GaN HEMT with TiN gate, it is also necessary to develop a metal-insulator semiconductor (MIS) or metal-oxidesemiconductor (MOS) HEMTs using SiO<sub>2</sub>, ZrO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub> and other oxides.

Another purpose of my research is to fabricate a kind of MIS-gate AlGaN/GaN HFET by using oxide/TiN stack structure or other dielectrics created by sputtering. By this approach, the interface between the oxide layer and the gate metal can be improved owing to the sample is kept in vacuum ambient environment. To achieve this proposal, it is necessary to find a suitable dielectric material which can stand annealing temperature at about 850°C.

### §1.4. Outline of thesis

This thesis reports on the Synthesis and Application of Oxide for Gallium Nitride Electron Devices. This thesis is divided into four parts:

In Chapter 2, we deposited the NiO films under different O<sub>2</sub>/Ar ratios and substrate temperatures, which are face-centered cubic crystalline structure. The NiO films possess direct bandgaps of 3.6, 3.2, 2.7, and 3.0 eV at O partial pressures of 15%, 25%, 50%, and 65%, respectively. The crystalline structure, composition, electrical and optical properties of the as-grown films depend on the substrate temperature. When the substrate temperature increasing, the crystalline quality and stoichiometric of NiO film were improved, resulting in higher bandgap value and resistivity. NiO film obtained at a substrate temperature of 30 °C shows the smallest resistivity, which is suitable for gate electrode for AlGaN/GaN HFETs. Besides, compared with the Ni/GaN Schottky diode, the turn-on voltage of the NiO/GaN heterojunction diode is relatively higher and shows a much smaller reverse leakage current.

In Chapter 3, we explored the temperature-dependent behavior of a NiO/GaN heterojunction diode in this work. The cubic crystalline structured NiO film exhibited p-type semiconducting behavior. The heterojunction diode showed an excellent stability over the temperature range of 25–175 °C. The turn-on voltage of the devices decreased from 2.2 to 1.5 V with increasing temperature. The device characteristics in forward bias were dominated by three types of current transport mechanisms and were found to be dependent on the applied bias voltages and temperature.

In Chapter 4, NiO film obtained at a substrate temperature of 30 °C shows the smallest resistivity and was used as gate electrode for AlGaN/GaN HFETs application. Compared with the Ni/Au-gated device, the band structure adjustment introduced by p-NiO gate was found to shift the threshold voltage positively and then cause a smaller drain current. The valence and conduction band offsets between NiO and GaN are estimated to be 1.25 eV and 1.42 eV using X-ray photoelectron spectroscopy.

After recess, the threshold voltage for the Ni- and NiO-gated HFETs has a positive shift with the smaller drain current density. With the recessed-gate structure, normally-off GaN HFETs can be obtained with a threshold voltage of closing to 0 V. Meanwhile, the

existence of p-type NiO gate layer can decrease the tunneling of electron and leakage current.

In Chapter 5, we fabricated the high-k material HfO<sub>x</sub>N<sub>y</sub> with different oxygen flow rates in the reactive sputtering ambient. It demonstrated that the surface morphologies, composition, and optical properties of the HfO<sub>x</sub>N<sub>y</sub> films were dependent on the oxygen flow rate in the O<sub>2</sub>/N<sub>2</sub>/Ar mixture sputtering ambient. The synthesis conditions had been also optimized. We focus on the thermally stable HfO<sub>x</sub>N<sub>y</sub> was deposit as gate dielectric for TiN/HfO<sub>x</sub>N<sub>y</sub>/AlGaN/GaN heterostructure field-effect transistors application. The obtained metal-oxide-semiconductor heterostructure field-effect transistors possessed a small hysteresis and a low leakage current by depositing HfO<sub>2</sub> and HfO<sub>x</sub>N<sub>y</sub> dielectric at different oxygen flow rates. After post deposition annealing at 900 °C, the device using HfO<sub>x</sub>N<sub>y</sub> dielectric operated normally with good pinch-off characteristics, while obvious degradation are observed for the HfO<sub>2</sub> gated one at 600 °C. This result shows that the HfO<sub>x</sub>N<sub>y</sub> dielectric is a promising candidate for the self-aligned gate process.

The conclusions of the dissertation and the future plans to improve the performance of the devices are given in Chapter 6.

### Chapter 1: Introduction

#### §1.5. Reference

- [1] Fromherz P, Kiessling V, Kottig K, et al. Membrane transistor with giant lipid vesicle touching a silicon chip[J]. Applied Physics A, 1999, 69(5): 571-576.

- [2] Bauer F, Streit P. Gate turn-off thyristor: U.S. Patent 5,491,351[P]. 1996-2-13.

- [3] Kurata M, Azuma M, Ohashi H, et al. Gate turn-off thyristors[M]//Semiconductor Devices for Power Conditioning. Springer, Boston, MA, 1982: 91-121.

- [4] Ye P D, Wilk G D, Kwo J, et al. GaAs MOSFET with oxide gate dielectric grown by atomic layer deposition[J]. IEEE Electron Device Letters, 2003, 24(4): 209-211.

- [5] Kitagawa M, Omura I, Hasegawa S, et al. A 4500 V injection enhanced insulated gate bipolar transistor (IEGT) operating in a mode similar to a thyristor[C]//Electron Devices Meeting, 1993. IEDM'93. Technical Digest., International. IEEE, 1993: 679-682.

- [6] Calame J P, Myers R E, Binari S C, et al. Experimental investigation of microchannel coolers for the high heat flux thermal management of GaN-on-SiC semiconductor devices[J]. International Journal of Heat and Mass Transfer, 2007, 50(23-24): 4767-4779.

- [7] Chow T P, Khemka V, Fedison J, et al. SiC and GaN bipolar power devices[J]. Solid-State Electronics, 2000, 44(2): 277-301.

- [8] Zolper J C. A review of junction field effect transistors for high-temperature and high-power electronics[J]. Solid-State Electronics, 1998, 42(12): 2153-2156.

- [9] Rumyantsev S L, Pala N, Shur M S, et al. Generation-recombination noise in GaN/AlGaN heterostructure field effect transistors[J]. IEEE Transactions on Electron Devices, 2001, 48(3): 530-534.

- [10] Gao G B, Morkoc H. Material-based comparison for power heterojunction bipolar transistors[J]. IEEE Transactions on Electron Devices, 1991, 38(11): 2410-2416.

- [11] Duboz J Y. GaN as seen by the industry [J]. physica status solidi (a), 1999, 176(1): 5-14.

- [12] Monemar B, Pozina G. Group III-nitride based hetero and quantum structures[J]. Progress in Quantum Electronics, 2000, 24(6): 239-290.

- [13] Nakamura S. The roles of structural imperfections in InGaN-based blue light-emitting diodes and laser diodes[J]. Science, 1998, 281(5379): 956-961.

- [14] Tsuda Y, Ohta M, Vaccaro P O, et al. Blue laser diodes fabricated on m-plane GaN

- substrates[J]. Applied physics express, 2008, 1(1): 011104.

- [15] Miyajima T, Tojyo T, Asano T, et al. GaN-based blue laser diodes[J]. Journal of Physics: Condensed Matter, 2001, 13(32): 7099.

- [16] Nakamura S, Mukai T, Senoh M. High-power GaN pn junction blue-light-emitting diodes[J]. Japanese Journal of Applied Physics, 1991, 30(12A): L1998.

- [17] Kikuchi A, Kawai M, Tada M, et al. InGaN/GaN multiple quantum disk nanocolumn light-emitting diodes grown on (111) Si substrate[J]. Japanese Journal of Applied Physics, 2004, 43(12A): L1524.

- [18] Watanabe A, Takeuchi T, Hirosawa K, et al. The growth of single crystalline GaN on a Si substrate using AIN as an intermediate layer[J]. Journal of crystal growth, 1993, 128(1-4): 391-396.

- [19] H. Ishikawa, K. Yamamoto, T. Egawa, T. Soga, T. Jimbo, M. Umeno, Thermal stability of GaN on (111) Si substrate, Journal of Crystal Growth, Volumes 189–190, 15 June 1998, Pages 178-182.

- [20] Ishikawa H, Yamamoto K, Egawa T, et al. Thermal stability of GaN on (111) Si substrate[J]. Journal of crystal growth, 1998, 189: 178-182.

- [21] Honda Y, Kuroiwa Y, Yamaguchi M, et al. Growth of GaN free from cracks on a (111) Si substrate by selective metalorganic vapor-phase epitaxy[J]. Applied Physics Letters, 2002, 80(2): 222-224.

- [22] Guha S, Bojarczuk N A. Ultraviolet and violet GaN light emitting diodes on silicon[J]. Applied Physics Letters, 1998, 72(4): 415-417.

- [23] Strite S, Ruan J, Li Z, et al. An investigation of the properties of cubic GaN grown on GaAs by plasma assisted molecular beam epitaxy[J]. Journal of Vacuum Science & Technology B: Microelectronics and Nanometer Structures Processing, Measurement, and Phenomena, 1991, 9(4): 1924-1929.

- [24] Kuznia J N, Yang J W, Chen Q C, et al. Low pressure metalorganic chemical vapor deposition of cubic GaN over (100) GaAs substrates[J]. Applied physics letters, 1994, 65(19): 2407-2409.

- [25] Okumura H, Misawa S, Yoshida S. Epitaxial growth of cubic and hexagonal GaN on GaAs by gas source molecular beam epitaxy[J]. Applied physics letters, 1991, 59(9): 1058-1060.

- [26] Sverdlov B N, Martin G A, Morkoc H, et al. Formation of threading defects in GaN

- wurtzite films grown on nonisomorphic substrates[J]. Applied Physics Letters, 1995, 67(14): 2063-2065.

- [27] Lin M E, Strite S, Agarwal A, et al. GaN grown on hydrogen plasma cleaned 6H-SiC substrates[J]. Applied physics letters, 1993, 62(7): 702-704.

- [28] Lin M E, Sverdlov B, Zhou G L, et al. A comparative study of GaN epilayers grown on sapphire and SiC substrates by plasma assisted molecular beam epitaxy[J]. Applied physics letters, 1993, 62(26): 3479-3481.

- [29] Zhao D G, Xu S J, Xie M H, et al. Stress and its effect on optical properties of GaN epilayers grown on Si (111), 6H-SiC (0001), and c-plane sapphire[J]. Applied physics letters, 2003, 83(4): 677-679.

- [30] Steckl A J, Devrajan J, Tran C, et al. SiC rapid thermal carbonization of the (111) Si semiconductor on insulator structure and subsequent metalorganic chemical vapor deposition of GaN[J]. Applied physics letters, 1996, 69(15): 2264-2266.

- [31] Yang J W, Sun C J, Chen Q, et al. High quality GaN–InGaN heterostructures grown on (111) silicon substrates[J]. Applied physics letters, 1996, 69(23): 3566-3568.

- [32] Kobayashi N P, Kobayashi J T, Dapkus P D, et al. GaN growth on Si (111) substrate using oxidized AlAs as an intermediate layer[J]. Applied physics letters, 1997, 71(24): 3569-3571.

- [33] Edgar J H. Properties, processing and applications of gallium nitride and related semiconductors[M]. Iet, 1999.

- [34]Gaska R, Yang J W, Osinsky A, et al. Electron transport in AlGaN–GaN heterostructures grown on 6H–SiC substrates[J]. applied physics letters, 1998, 72(6): 707-709.

- [35] Smorchkova I P, Elsass C R, Ibbetson J P, et al. Polarization-induced charge and electron mobility in AlGaN/GaN heterostructures grown by plasma-assisted molecular-beam epitaxy[J]. Journal of Applied Physics, 1999, 86(8): 4520-4526.

- [36] Hsu L, Walukiewicz W. Effect of polarization fields on transport properties in AlGaN/GaN heterostructures[J]. Journal of Applied Physics, 2001, 89(3): 1783-1789.

- [37] Qiao D, Yu L S, Lau S S, et al. Dependence of Ni/AlGaN Schottky barrier height on Al mole fraction[J]. Journal of Applied Physics, 2000, 87(2): 801-804.

- [38] Lee M L, Sheu J K, Lai W C, et al. Characterization of GaN Schottky barrier photodetectors with a low-temperature GaN cap layer[J]. Journal of applied physics, 2003,

94(3): 1753-1757.

[39] Kao C J, Chen M C, Tun C J, et al. Comparison of low-temperature GaN, SiO<sub>2</sub>, and SiN<sub>x</sub> as gate insulators on AlGaN/GaN heterostructure field-effect transistors[J]. Journal of applied physics, 2005, 98(6): 064506.

[40] Li L, Kishi A, Liu Q, et al. Gan schottky barrier diode with tin electrode for microwave rectification[J]. IEEE Journal of the Electron Devices Society, 2014, 2(6): 168-173.

# Chapter 2: Synthesis and characterization of NiO

#### §2.1. Selection of material

In today's rapid development of science and technology, the requirements for new materials are also increasing. The traditional and single materials can no longer meet the needs of the progress of the times. Looking for new materials with excellent performance can break the inherent limitations of old materials to meet the needs of scientific and technological development. Materials such as semiconductors, metals, ceramics and polymers are now developed rapidly. In particular, the development of semiconductor materials have brought human into the information age. Without semiconductor materials, there would be not computer technology, and modern people have not a rich and colorful lives. In the human society, semiconductor materials have developed more than one century, which has gone through leapfrog development with three generations. The thirdgeneration semiconductor materials represented by GaN and SiC are still in the developmental stage [1-4]. The third-generation semiconductor materials can more meet the requirements of the modern electronic technology with high-temperature and highfrequency performance. However, these materials have some obvious problems in the field of optoelectronic devices and microelectronic devices, such as the difficulty of commercialization for large-size substrates, excessive temperature in the preparation of materials, and the reliability and stability of p-type materials, all of which have caused people to research, develop and design new materials according to predetermined performance.

There are several p-type materials, such as p-type GaN, Cu<sub>2</sub>O, NiO, and so on. GaN is doped with Mg to form p-type GaN at the temperature of about 1010 °C [5]. It has low carrier concentration of approximately 10<sup>17</sup>/cm<sup>3</sup>. Cu<sub>2</sub>O is a natural p-type material, which is fabricated at room temperature with low carrier concentration of approximately 10<sup>17</sup>/cm<sup>3</sup>. But Cu<sub>2</sub>O is instable with easily oxidizing into CuO [6]. NiO is also a natural p-type material with synthesis under room temperature. It has high carrier concentration of approximately 10<sup>18</sup>/cm<sup>3</sup>, which can as much as possible deplete 2DEG of HFETs to form normally-off devices. So NiO is an expected material.

NiO is a 3d transition metal oxide [7-8] and a typical direct wide bandgap p-type

semiconductor. The bandgap of the NiO film is usually 3.6eV~4.0eV [9-11]. The basic physical properties in shown in Table 2-1. Due to its unique electronic structure, NiO has shown excellent application prospects in many fields such as transparent conductive films, gas sensors, UV detectors and electrochromic devices, etc. [11-18].

NiO is a p-type semiconductor with a wide range of applications, such as nonvolatile memory devices, as a functional layer material in chemical sensors, transparent conductive films, UV photodetector and electrochromic devices. NiO is a promising material applicable to nonvolatile memory devices due to its high on/off ratio and simple constituents. In recent years, the photocatalytic degradation of various kinds of organic and inorganic pollutants using semiconductor powders as photocatalysts has been extensively studied NiO can be doped into semiconductors, such as TiO<sub>2</sub>, InVO<sub>4</sub>, NaTaO<sub>3</sub>, etc., as photocatalyst [19-20]. Due to its excellent performance, NiO is used to fabricate transparent p-NiO/n-ZnO heterojunction devices for ultraviolet photodetectors [21]. The p-NiO/n-ZnO heterojunction device has an average transmittance of over 80% in the visible region. The p-NiO/n-ZnO heterojunction device can detect ultraviolet light by the application of reverse bias. As a typical natural p-type semiconductor material, NiO has attracted many researchers due to its special properties and wide application.

| Name                                               | NiO                                                                                                   |  |  |

|----------------------------------------------------|-------------------------------------------------------------------------------------------------------|--|--|

| Relative density                                   | 6.6-6.8                                                                                               |  |  |

| Melting point                                      | 1984 °C                                                                                               |  |  |

| Molecular mass                                     | 74.7 g.mal-1                                                                                          |  |  |

| Band-gap                                           | 3.6-4.0 eV                                                                                            |  |  |

| Conduction type                                    | direct-band-gap p-type                                                                                |  |  |

| Solubleness                                        | insoluble in water and lye, soluble in acid, ammonia, hot perchloric acid and hot sulfuric acid, etc. |  |  |

| Table 2-1 The physical properties of the NiO film. |                                                                                                       |  |  |

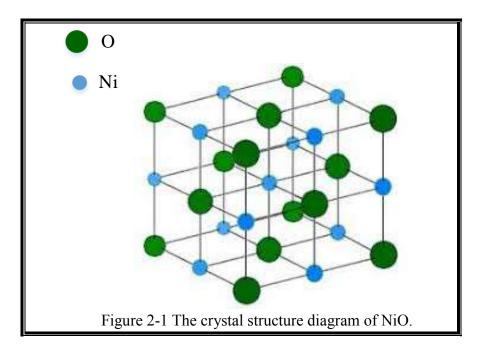

The usual stable NiO structure belongs to the Fm3m space group of cubic crystal system with the same crystal structure as NaCl. The distance between  $\mathrm{Ni^{2+}}$  and the nearest  $\mathrm{O^{2-}}$  is a×10<sup>-8</sup> cm and the lattice constant is a=b=c=0.418 nm [22]. Figure 2-1 shows a diagram of the common NiO crystal structure. The stoichiometric ratio of Ni to O obtained by different preparation methods is different from the normal case. However, to

sum up there are basically NiO, Ni<sub>2</sub>O<sub>3</sub> and Ni<sub>3</sub>O<sub>4</sub> or their mixture, where it is dominated by NiO, Ni<sub>2</sub>O<sub>3</sub> and their mixture. Ni<sub>2</sub>O<sub>3</sub> is usually the dark brown solid, which is converted directly to NiO after high temperature treatment [23].

NiO has the closely matched lattice constants and bandgap energy (3.6 eV) with GaN, which makes NiO as a promising candidate for applications in GaN-based heterojunction devices. Furthermore, the natural p-type NiO can reduce the amount of field crowding as guard ring at the main junction, which is an effective method obtain high breakdown voltage. In this thesis, NiO thin film was prepared by magnetron reactive sputtering on an n-GaN/sapphire substrate to form the NiO/GaN heterojunction diode.

### §2.2. The synthesis of NiO

#### §2.2.1. The synthesis of NiO films with different oxygen ratio

In this experiment, the n-GaN layers were deposited on (0001) sapphire substrate by MOCVD. The standard photolithography and lift-off technology were utilized to form both ohmic and Schottky contacts. The cathode ohmic contact was constituted by a Ti/Al/Ti/Au (50/200/40/40 nm) multi-layer structure followed by annealing at 800 °C in N<sub>2</sub> atmosphere for 1 min. Before Schottky deposition, the samples were surface-cleaned

by O<sub>2</sub> plasma ashing and then immersed in diluted HCl (HCl:H<sub>2</sub>O=1:1) solution for 5 min to remove the possible oxide layer after lithography. NiO film was deposited by reactive sputtering (RF, 75 W) in different O percentage of 15%, 25%, 50%, and 65%, using a metal target of Ni. A NiO/Ni/Au (30/10/40 nm) stack film was deposited for anode Schottky electrode. For comparison, sample with Ni/Au (30/40 nm) electrode was also deposited by RF sputtering in Ar atmosphere under a sputtering power of 150 W and a chamber pressure of 0.14 Pa. Finally, the samples were treated by post-annealing at 300 °C in N<sub>2</sub> atmosphere for 10 min.

### §2.2.2. The synthesis of NiO films at different substrate temperatures

In order to evaluate the influence of substrate temperature on the material performance, NiO films were first formed on double-sides polished sapphire substrates using reactive sputtering. A nominal 100 nm NiO layer was deposited under different substrate temperatures of 30, 100, 200 and 300 °C, respectively, in Ar and O<sub>2</sub> (Ar:O<sub>2</sub>=15:5 sccm) mixed ambient with a Ni target. The sputtering power was fixed at 75 W with a chamber pressure of about 0.13 Pa. The sputtering target was firstly cleaned in Ar atmosphere for 10 min with a sputtering power of 150 W. In this study, X-ray diffraction (XRD), X-ray photoelectron spectroscopy (XPS), and UV-Vis absorption spectrum were utilized to characterize the structure, morphology, and optical properties of the as-deposited NiO films.

# §2.3. The characteristics of NiO films

#### §2.3.1. The properties of NiO films with different oxygen ratio

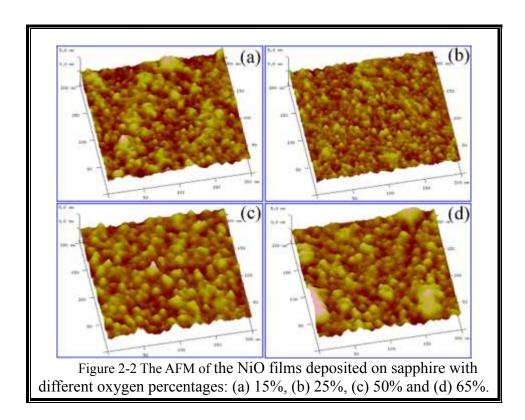

NiO film (approximately 100 nm) was deposited on a polished sapphire substrate using different oxygen percentage of 15%, 25%, 50% and 65% at room temperature for the x-ray diffraction (XRD), atomic force microscope (AFM) and optical transmittance measurements.

The surface morphology and the root mean square roughness (RMS) of NiO films with different oxygen percentages are characterized using AFM (as shown in Figure 2-2) which is scanned in an area of 0.2μm×0.2 μm. With the low oxygen percentage, the surface of the samples consist with high density and small size particle (Figure 2-2 a and b). The RMS of those samples are approximately 0.35 and 0.29 nm, respectively. For the sample deposited with the oxygen percentage of 50%, the grain size increased obviously (Figure 2-2 c) and its RMS is about 0.37 nm. Finally, Figure 2-2 d showed the most rough morphology with a RMS of approximately 0.46 nm for the film with 65% oxygen percentage. Therefore, the surface of the film with 25% oxygen percentage is the most flat. The sputtered NiO on the sapphire substrate with high oxygen percentage will has the deterioration of the film quality. The oxidation of the Ni target is very weak at a relatively low oxygen percentage. The sputtered Ni atoms has enough time to diffuse and react from the target surface to substrate surface, resulting in a better surface roughness. While, the oxidization of metal target surface is much easier at a relatively high oxygen percentage, which suggest there are not enough Ni atoms to escape from the target and react with O atoms to deposit on the substrate.

Usually, the first several nanometers of film deposited by sputtering is amorphous,

which can serve as the stress buffer layer for lattice mismatch. Besides, the room temperature sputtering is also helpful to reduce the thermal stress between the film and substrate. Therefore, we think the influence of stress on the XRD measurement is relatively weak. In the XRD spectrum (Figure 2-3) for the samples with the low oxygen percentage (15% and 25%), two peaks are generally observed at around 37.5° and 78.2°, which are assigned to the face-centered cubic crystalline diffraction patterns of (111) and (222) respectively [24]. With the increase of the oxygen percentage (50%), the crystalline texture is changed, which a more peak of (220) is appeared at around 65.3°. While for the film with the oxygen percentage of 65%, it is dominated by (111) which is also assigned to the face-centered cubic crystalline diffraction pattern. As the oxygen percentage increasing, the peaks became broad and weak, which suggested the crystalline quality is deteriorated. Using the full-width at half maximum (FWHM) of (111) peak, the mean grain size of the film is estimated by Scherrer formula as following [25]:

$$D = K \frac{\lambda}{\beta cos\theta} \tag{2-1}$$

Where D is the diameter of the grain, K=0.89 is the Scherrer constant,  $\lambda$ =0.154 nm is the wavelength of the X-ray,  $\beta$  is the FWHM of the peak and  $\theta$  is the Bragg diffraction angle. From Figure 2-3 it is observed that the FWHM increases with increasing the oxygen percentages, which indicates the mean grain size of the films increases. It accord with the result of AFM. We calculated the mean grain size of the film with oxygen percentages of 25% is approximately 3.7 nm.

The optical properties of the films are characterized by UV-Visible transmission spectra. The NiO films with different oxygen percentages is grown on the double polished sapphire in order to obtain exact results by magnetron sputtering (the inset in Figure 2-4). Figure 2-4 shows optical transmittance spectra of the deposited NiO films (approximately 100 nm) at various oxygen percentages. It can be clearly observed absorption coefficient as a function of photon energy. The following equation can calculate absorption coefficient [26]:

$$T = C\exp(-\alpha t) \tag{2-2}$$

Where T is the transmittance of the film,  $\alpha$  is absorption coefficient, C is a constant, and t is the film thickness (approximately 100 nm). Because of the negligible reflectivity near the absorption edge, C is approximately in unity. The absorption tail of the NiO films with different oxygen ratio is shown in Table 2-3. With the oxygen ratio increasing from 15% to 50%, the absorption tail increasing from 346 nm to 459 nm, which suggests that the absorption of the film moves to the visible direction. As the oxygen content continues to increase, the absorption tail decreases to 417 nm. By applying the following Tauc model and the Davis and Mott model, the optical band gap ( $E_g$ ) of the films was extracted from the absorption edge [27].

$$\alpha h \nu = D(h \nu - E_g)^n \tag{2-3}$$

Where Eg is the optical band gap, D is a constant, and h is the photon energy. Here, n is 1/2 because of the direct bandgap of NiO films. The optical band gap of the film was extracted from absorption edge by applying the Tauc model, and the Davis and Mott model. By extrapolating the linear part to the zero absorption coefficients, we obtained the  $E_g$  value. As shown in Table 2-3, with increasing oxygen percentage from 15% to 50%, the band gap of the films decreases from 3.58 to 2.7 eV and increased by 2.97 eV at a higher oxygen percentage of 65%. As shown in XRD spectra, the bandgap increase for 65% oxygen is not very clear because maybe the crystalline structure is the changed, which is dominated by (111) texture. While it is shown a (111) and (220) texture for the film deposited with 50% oxygen. Meanwhile, the absorption edge for the samples with high oxygen percentage (50% and 65%) are not very clear, which can cause no exact calculation of the band gap.

| Oxygen ratio | Absorption tail (nm) | Bandgap<br>(eV) |

|--------------|----------------------|-----------------|

| 15%          | 346                  | 3.58            |

| 25%          | 387                  | 3.2             |

| 50%          | 459                  | 2.7             |

| 65%          | 417                  | 2.97            |

Table 2-3 The absorption tail and bandgap of the NiO films with different oxygen percentages.

The magnetron sputtering has the potentials of large area, good uniformity, and easy to obtain stack electrode. For reactive sputtering method, the structural, electrical, and optical properties of the NiO are usually dependent on the oxygen partial pressure, power, substrate temperature, and so on [28, 29]. However, many works also suggest that the preferred orientation and crystalline quality of NiO film show a relationship with the substrate temperature [28].

#### §2.3.2. The properties of NiO films with different substrate temperatures

By analyzing the normalized XRD patterns of the NiO samples grown at different growth temperatures (Figure 2-5), two diffraction peaks at around 36.8°, and 78.3° dominate the spectra, which are indexed to the face-centered cubic crystalline diffraction patterns of NiO (111) and (222), respectively [30]. With the substrate temperature increasing from 30 to 200 °C, the diffraction peaks are intensified with a smaller FWHM value. Besides, the diffraction peaks show obvious movement towards higher 2-theta (20) values with the increasing temperature. Usually, the reaction between the Ni and O<sub>2</sub> was insufficient when the substrate temperature was low, the high density of interstitial oxygen and Ni vacancies in the film will cause the deterioration of crystalline quality (expansion of lattice parameter) and non-stoichiometric film. While for higher substrate temperature, atoms arriving at the substrate surface will possess higher kinetic energy, which is beneficial for the migration and reaction to obtain a better crystalline quality.

The movement towards higher  $2\theta$  values of the XRD peaks indicate an improvement in the crystalline quality of the NiO film (close to the stoichiometric status). However, the enhancement of crystalline quality (intensity and FWHM) is inconspicuous at the temperature of 300 °C because of the decomposition of NiO as shown in the following XPS measurements [31].